Beyond CMOS

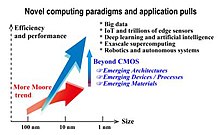

Beyond CMOSrefers to the possible futuredigital logictechnologies beyond thescaling limitsofCMOStechnology.[1][2][3][4]which limits device density and speeds due to heating effects.[5]

Beyond CMOSis the name of one of the 7 focus groups inITRS 2.0(2013) and in its successor, theInternational Roadmap for Devices and Systems.

CPUs using CMOS were released from 1986 (e.g. 12 MHzIntel 80386). As CMOS transistor dimensions were shrunk the clock speeds also increased. Since about 2004 CMOS CPU clock speeds have leveled off at about 3.5 GHz.

CMOS devices sizes continue to shrink – seeIntel tick–tockandITRS:

- 22 nanometerIvy Bridgein 2012

- first14 nanometerprocessors shipped in Q4 2014.

- In May 2015, Samsung Electronics showed a 300 mm wafer of10 nanometerFinFETchips.[7]

It is not yet clear if CMOS transistors will still work below 3 nm.[4]See3 nanometer.

Comparisons of technology

[edit]About 2010 theNanoelectronic Research Initiative(NRI) studied various circuits in various technologies.[2]

Nikonov benchmarked (theoretically) many technologies in 2012,[2]and updated it in 2014.[8]The 2014 benchmarking included 11 electronic, 8spintronic,3orbitronic,2ferroelectric,and 1straintronicstechnology.[8]

The 2015ITRS 2.0report included a detailed chapter onBeyond CMOS,[9]covering RAM and logic gates.

Some areas of investigation

[edit]- Magneto-Electric Spin-Orbitlogic[10]

- tunnel junctiondevices, egTunnel field-effect transistor[11]

- indium antimonidetransistors

- carbon nanotube FET,eg CNTTunnel field-effect transistor

- graphene nanoribbons

- molecular electronics

- spintronics— many variants

- future low-energy electronics technologies,ultra-low dissipation conduction paths, including

- photonicsandoptical computing

- superconducting computing

Superconducting computing and RSFQ

[edit]Superconducting computingincludes several beyond-CMOS technologies that use superconducting devices, namely Josephson junctions, for electronic signals processing and computing. One variant calledrapid single-flux quantum(RSFQ) logic was considered promising by the NSA in a 2005 technology survey despite the drawback that available superconductors require cryogenic temperatures. More energy-efficient superconducting logic variants have been developed since 2005 and are being considered for use in large scale computing.[12][13]

See also

[edit]- International Technology Roadmap for Semiconductors

- International Roadmap for Devices and Systems

- Moore's law

- MOSFET scaling

- Nanostrain,a project to characterise piezoelectric materials for low power switches

- S-PULSE,the EU Shrink-Path of Ultra-Low Power Superconducting Electronics initiative

- Probabilistic complementary metal-oxide semiconductor (PCMOS)

References

[edit]- ^"Extending the road beyond CMOS. Hutchby 2002"(PDF).Archived(PDF)from the original on 2022-12-06.Retrieved2023-04-16.

- ^abcNikonov, Dmitri E.; Young, Ian A. (September 2012). "Overview of Beyond-CMOS Devices and A Uniform Methodology for Their Benchmarking".arXiv:1302.0244[cond-mat.mes-hall].

- ^Bernstein; et al. (2011)."Device and Architecture Outlook for Beyond CMOS Switches".Archivedfrom the original on 2015-02-22.Retrieved2015-02-22.

{{cite journal}}:Cite journal requires|journal=(help) - ^ab"Review of Advanced and Beyond CMOS FET Technologies for Radio Frequency Circuit Design. Carta 2011"(PDF).Archived fromthe original(PDF)on 2015-02-23.Retrieved2015-02-23.

- ^Frank, D.J. (March 2002). "Power-constrained CMOS scaling limits".IBM Journal of Research and Development.46(2.3): 235–244.CiteSeerX10.1.1.84.4043.doi:10.1147/rd.462.0235.

- ^"Beyond CMOS"(PDF).The International Roadmap for Devices and Systems (2017 ed.). IEEE. 2018.Archived(PDF)from the original on 2018-07-03.Retrieved2018-07-03.

- ^"Samsung vows to start 10nm chip production in 2016".23 May 2015.Archivedfrom the original on 16 July 2015.Retrieved16 July2015.

- ^abNikonov; Young (2015)."Benchmarking of Beyond-CMOS Exploratory – Devices for Logic Integrated Circuits".IEEE Journal on Exploratory Solid-State Computational Devices and Circuits.1:3–11.Bibcode:2015IJESS...1....3N.doi:10.1109/JXCDC.2015.2418033.

- ^Beyond CMOS(PDF).International Technology Roadmap for Semiconductors 2.0 (2015 ed.).Archived(PDF)from the original on 2023-04-16.Retrieved2017-06-16.

- ^Manipatruni, Sasikanth; Nikonov, Dmitri E.; Lin, Chia-Ching; Gosavi, Tanay A.; Liu, Huichu; Prasad, Bhagwati; Huang, Yen-Lin; Bonturim, Everton; Ramesh, Ramamoorthy; Young, Ian A. (2018-12-03)."Scalable energy-efficient magnetoelectric spin–orbit logic".Nature.565(7737): 35–42.doi:10.1038/s41586-018-0770-2.ISSN0028-0836.PMID30510160.S2CID256769872.

- ^Seabaugh (September 2013)."The Tunneling Transistor".IEEE Spectrum.50(10). IEEE: 35–62.doi:10.1109/MSPEC.2013.6607013.S2CID2729197.Archivedfrom the original on 2021-06-29.Retrieved2023-04-16.

- ^Holmes, D.S.; Ripple, A.L.; Manheimer, M.A. (June 2013)."Energy-efficient superconducting computing—power budgets and requirements".IEEE Trans. Appl. Supercond.23(3). 1701610.Bibcode:2013ITAS...2301610H.doi:10.1109/TASC.2013.2244634.S2CID20374012.Archivedfrom the original on 2022-10-10.Retrieved2023-04-16.

- ^Holmes, D.S.; Kadin, A.M.; Johnson, M.W. (December 2015)."Superconducting Computing in Large-Scale Hybrid Systems".Computer.48(12): 34–42.doi:10.1109/MC.2015.375.S2CID26578755.Archivedfrom the original on 2022-12-25.Retrieved2023-04-16.

Further reading

[edit]- Banerjee, Niloy (2019-09-03)."New Door in the" Beyond CMOS "World".BISinfotech.Archivedfrom the original on 2022-05-13.Retrieved2022-05-13.

- Nikonov, Dmitri E.;Ian A.(2013-12). "Overview of Beyond-CMOS Devices and a Uniform Methodology for Their Benchmarking".Proceedings of the IEEE.101(12): 2498–2533.doi:10.1109/jproc.2013.2252317.ISSN0018-9219.

- Seabaugh, A.C. and Zhang, Q., 2010. Low-voltage tunnel transistors for beyond CMOS logic.Proceedings of the IEEE,98(12), pp.2095-2110.

- Bernstein, K., Cavin, R.K., Porod, W., Seabaugh, A. and Welser, J., 2010. Device and architecture outlook for beyond CMOS switches.Proceedings of the IEEE,98(12), pp.2169-2184.

- Sasikanth Manipatruni,Nikonov, D.E. andIan A. Young,2018. Beyond CMOS computing with spin and polarization.Nature Physics,14(4), pp.338-343.

- Banerjee, S.K., Register, L.F., Tutuc, E., Basu, D., Kim, S., Reddy, D. and MacDonald, A.H., 2010. Graphene for CMOS and beyond CMOS applications.Proceedings of the IEEE,98(12), pp.2032-2046.

- Topaloglu, R.O. and Wong, H.S.P. eds., 2019.Beyond-CMOS technologies for next generation computer design.Berlin/Heidelberg, Germany: Springer.

- Sasikanth Manipatruni,Nikonov, D.E., Lin, C.C., Gosavi, T.A., Liu, H., Prasad, B., Huang, Y.L., Bonturim, E., Ramesh, R. and Young, I.A., 2019. Scalable energy-efficient magnetoelectric spin–orbit logic.Nature,565(7737), pp.35-42.