CMOS

CMOS( シーモス, Complementary Metal-Oxide-Semiconductor; tương bổ hình MOS ) とは, P hình とN hình のMOSFETをディジタル hồi lộ(Luận lý hồi lộ) で tương bổ đích に lợi dụng する hồi lộ phương thức[ chú 釈 1],およびそのような điện tử hồi lộ やICのことである[1].また, そこから phái sinh し đa nghĩa đích に đa くの dụng lệ が quan られる ( 『#その tha の dụng lệ』 tham chiếu ).

Tương bổ hình MOS ( CMOS ) プロセスは,フェアチャイルドセミコンダクターXã のフランク・ワンラスが khảo án し, dực 1963 niên にワンラスとチータン・サーが học hội で phát biểu したのが thủy まりである. RCA xã は1960 niên đại hậu bán に “COS-MOS” という thương tiêu で thương phẩm hóa し[2],Tha のメーカーに biệt の danh xưng を tham させ, 1970 niên đại tiền bán には “CMOS” が tiêu chuẩn đích な danh xưng となるに chí った.

CMOSは, 1980 niên đại にNMOSロジックを bạt いてVLSI dụng MOSFETの chủ lưu となり, TTL (Transistor-transistor logic) kỹ thuật も trí き hoán えた[3].その hậu, CMOSはVLSIチップに đáp tái されるMOSFET bán đạo thể デバイスの tiêu chuẩn đích な chế tạo プロセスであり続けている. 2011 niên hiện tại, ほとんどのデジタル, アナログ, ミックスドシグナルICを hàm むICチップがCMOS kỹ thuật で chế tạo されている.

CMOSデバイスの trọng yếu な đặc tính は, cao い nại ノイズ tính と đê い tĩnh đích điện lực tiêu phí である. MOSFETのペアのうち1つのトランジスタは thường にオフであるため, trực liệt の tổ み hợp わせはオンとオフを thiết り thế える tế に thuấn gian đích に đại きな điện lực を tiêu phí するだけである. そのため,NMOSロジックやTTLのように, trạng thái 変 hóa していないときにも định thường điện lưu が lưu れる luận lý hồi lộ ほど phát nhiệt せず, チップ thượng に cao mật độ に tập tích できる. CMOSがVLSIチップの thật trang kỹ thuật として tối も quảng く sử われるようになったのは, chủ にこのような lý do によるものである[4].

MOSとはMetal ( kim chúc ) -Oxide ( toan hóa mô ) -Semiconductor ( bán đạo thể ) の lược で, MOS hình điện giới hiệu quả トランジスタの vật lý đích cấu tạo のことを chỉ す. Toan hóa mô tuyệt duyên thể の thượng に kim chúc ゲート điện cực を trí き, さらにその thượng に bán đạo thể tài liêu を trí いたものである[1].かつてはゲート điện cực としてアルミニウムが sử われていたが, hiện tại はポリシリコンが sử われている[5].IBMやインテルが45ナノメートル・ノード[6]Dĩ hạ のサイズで phát biểu したように, CMOSプロセスにおける “Cao dụ điện suất ( high-k ) / kim chúc ゲート” の đăng tràng により, nhất bộ で kim chúc ゲートが phục hoạt している[7].

CMOSは thường にエンハンスメントモードMOSFET ( ngôn い hoán えれば, ゲート-ソース gian điện áp がゼロの tràng hợp, トランジスタがオフになる ) を sử dụng する[8].

Nguyên lý[Biên tập]

CMOS hồi lộ は, p hình とn hình の kim chúc - toan hóa mô - bán đạo thể điện giới hiệu quả トランジスタ (MOSFET) を tương bổ đích に tổ み hợp わせて, luận lý ゲートやその tha のデジタル hồi lộ を thật trang するものである[1].

Tối も cơ bổn đích な luận lý ゲートであるNOTゲート( luận lý phản 転 ) を hữu đồ に kỳ す. この hồi lộ において, VddとVssは điện nguyên tuyến ( VddはVssに đối して3〜15V trình độ の điện vị soa を trì つ ) で, Aが nhập lực tín hào tuyến である. Vdd trắc ( đồ trung thượng trắc ) がPMOS-FETでありVss trắc ( đồ trung hạ trắc ) がNMOS-FETである.

AがVssと đồng じ điện vị を trì つとき, thượng のFETがオンになり, hạ のFETがオフになる. このため, xuất lực Qの điện vị はVddとほぼ đẳng しくなる. また, AがVddと đồng じ điện vị を trì つとき, thượng のFETがオフになり, hạ のFETがオンになる. このため, xuất lực Qの điện vị はVssとほぼ đẳng しくなる. つまり, Aと phản đối の điện vị がQに hiện れる sự になる.

Lịch sử[Biên tập]

Tương bổ hình hồi lộ[Biên tập]

Tương bổ hình hồi lộ の nguyên lý は, 1953 niên にジョージ・クリフォード・シクライによってシクライ・ペア( Sziklai pair ) として sơ めて thiệu giới された. シクライ・ペアは,ダーリントン tiếp 続と đồng dạng に tăng phúc độ を tăng やしてベース điện lưu を giảm らすためのものであった. しかし, ダーリントン tiếp 続と vi ってNPNトランジスタとPNPトランジスタを tổ み hợp わせるという tương bổ hìnhバイポーラトランジスタHồi lộ であった[9].その hậu, いくつかの tương bổ hình hồi lộ について nghị luận された.

1962 niên には, đồng じくRCA xã のポール・K・ウェイマーが, CMOSに cận いBạc mô トランジスタ( TFT ) tương bổ hình hồi lộ を phát minh した[10].Bỉ は, tương bổ hìnhフリップフロップHồi lộ とインバータ hồi lộを phát minh したが, より phục tạp な tương bổ hình luận lý の nghiên cứu はしていない. pチャネルとnチャネルのTFTを đồng nhất cơ bản thượng の hồi lộ に nhập れたのは bỉ が tối sơ である. その3 niên tiền には,ジョン・T・ウォールマークとサンフォード・M・マーカスが,JFETを sử った tập tích hồi lộ として, tương bổ hình メモリ hồi lộ を hàm むさまざまな phục tạp な luận lý cơ năng を phát biểu している.フランク・ワンラスは, RCAでウェイマーが hành った nghiên cứu に tinh thông していた.

MOSFETの đăng tràng[Biên tập]

MOSFET( kim chúc - toan hóa mô - bán đạo thể điện giới hiệu quả トランジスタ, MOSトランジスタ ) は, 1959 niên にベル nghiên cứu sởのモハメド・M・アタラ とダウォン・カーンによって phát minh された[11].MOSFETの chế tạo プロセスには, もともとPMOS ( p hình MOS ) とNMOS ( n hình MOS ) の2 chủng loại があり, いずれもMOSFETを phát minh した đương thời のアタラとカーンが1960 niên にゲート trường 20μmを khai phát し, その hậu 10μmのPMOS, NMOSデバイスを khai phát したものである. MOSFETは đương sơ, バイポーラトランジスタを ưu tiên していたベル nghiên cứu sở では kiến quá ごされ vô thị されていたが, MOSFETの phát minh はフェアチャイルドセミコンダクターで đại きな quan tâm をよんだ. アタラの nghiên cứu に cơ づいて,チータン・サーが1960 niên hậu bán に chế tạo したMOS chế ngựTứ cực chân không quảnでフェアチャイドにMOS kỹ thuật を đạo nhập した[11].

CMOSの đăng tràng[Biên tập]

PMOSとNMOSの lạng プロセスを tổ み hợp わせた tân しいタイプのMOSFETロジックが, フェアチャイルドのフランク・ワンラスとチータン・サーによって khai phát され, コンプリメンタリーMOS (CMOS) と hô ばれるようになった[12].1963 niên 2 nguyệt に luận văn として phát biểu された. その luận văn とワンラスが xuất nguyện した đặc hứa では, シリコン cơ bản を nhiệt toan hóa してドレイン tiếp điểm とソース tiếp điểm の gian に nhị toan hóa ケイ tố の tằng を tác ることを cơ bổn として, CMOSデバイスの chế tạo phương pháp を khái thuyết している.

CMOSは1960 niên đại hậu bán にRCAXã によって thương nghiệp hóa された. RCAは tập tích hồi lộ ( IC ) の thiết kế にCMOSを thải dụng し, 1965 niên に không quân のコンピュータのためにCMOS hồi lộ を khai phát し, 1968 niên には288ビットのCMOS SRAMメモリチップを khai phát した[13].RCAは1968 niên に4000シリーズの tập tích hồi lộ にCMOSを thải dụng し, 20μmの bán đạo thể chế tạo プロセスから thủy め, その hậu sổ niên gian で10μmのプロセスに từ 々に拡 trương した. Đương sơ の4000シリーズは tối đại 1 MHzのクロックでしか động tác しなかった. Nhất phương, đương thời のTTLは, 10 MHzで động tác khả năng だったので, đương thời のCMOSは tốc độ tính năng đích に bất thập phân だったことは phủ めない[2].

CMOSの phát triển[Biên tập]

CMOS kỹ thuật は, đương sơ アメリカの bán đạo thể nghiệp giới では, đương thời より cao tính năng だったNMOSを ưu tiên して kiến quá ごされていた. しかし, CMOSは đê tiêu phí điện lực であることから nhật bổn の bán đạo thể メーカーにいち tảo く thải dụng され, さらに tiến hóa し, nhật bổn の bán đạo thể sản nghiệp の long thịnh につながった. Đông chi は1969 niên に thông thường のCMOSよりも đê tiêu phí điện lực で cao tốc động tác する hồi lộ kỹ thuật C²MOS ( Clocked CMOS ) を khai phát した[14].Đông chi はC²MOSの kỹ thuật を dụng いて, 1971 niên に khai phát され1972 niên に phát mại されたシャープのLEDポケット điện trác “エルシーミニ” のLSI ( đại quy mô tập tích hồi lộ ) チップを khai phát した. Tưu phóng tinh công xá ( hiện セイコーエプソン ) は1969 niên からセイコークォーツ oản thời kế のCMOS ICチップの khai phát を thủy め, 1971 niên にセイコーアナログウオッチ38SQWを phát mại して đại lượng sinh sản を khai thủy した[15].Dân sinh dụng として sơ めて lượng sản されたCMOS chế phẩm は, 1970 niên に phát mại されたハミルトンのデジタル oản thời kế “パルサー タイム・コンピューター” である[16].Tiêu phí điện lực の thiếu なさから, 1970 niên đại dĩ hàng, điện trác や thời kế にCMOSロジックが quảng く sử われるようになった.

1970 niên đại tiền bán の sơ kỳ のマイクロプロセッサはPMOSロジックで tác られており, PMOSロジックが sơ kỳ のマイクロプロセッサ nghiệp giới を chi phối していた. Thế giới sơ のマイクロコンピュータIntel 4004と thế giới sơ の phiếm dụng マイクロコントローラTMS1000は, PMOSロジックであった. CMOSを sử ったマイクロプロセッサは1975 niên にIntersil 6100とRCA CDP 1801として đăng tràng したが, マイクロプロセッサの thế giới でCMOSが chủ lưu になるのは1980 niên đại に nhập ってからである.

Sơ kỳ のCMOSはNMOSロジックより trì かったため, 1970 niên đại のコンピュータにはNMOSロジックがより quảng く sử dụng されていた. CMOSメモリチップ Intel 5101 ( 1Kbit SRAM ) のアクセス thời gianは800ns[17]だったのに đối し, đương thời tối tốc のNMOS (HMOS) メモリチップ Intel 2147 ( 4Kbit SRAM ) ( 1976 niên ) のアクセス thời gian は55/70ns[18]と dao かに cao tốc であった.

1978 niên, Masuhara Toshiakiが suất いる nhật lập の nghiên cứu チームは, ツインウェルHi-CMOSプロセスを đạo nhập し, 3μmプロセスで chế tạo したメモリチップ HM6147 ( 4Kbit SRAM ) を phát biểu した[19].HM6147のアクセス thời gian は35/45/55ns[20]なので, Intel 2147の55/70ns[18]より cao tốc である. HM6147の tiêu phí điện lưu は5Vで tối đại 80mA[20]であり, Intel 2147の5Vで tối đại 180mA[18]と bỉ べて đại phúc に tước giảm することに thành công した[ chú 釈 2].ついにCMOSはNMOSロジックの tính năng を siêu えた. Đồng đẳng あるいはそれ dĩ thượng の tính năng で tiêu phí điện lực が đại phúc に thiếu ないツインウェルCMOSプロセスは, tối chung đích にNMOSを bạt いて1980 niên đại のコンピュータ dụng bán đạo thể chế tạo プロセスとして tối も nhất bàn đích なものになった.

1989 niên に mộc tinh の quỹ đạo を chu hồi したNASAのガリレオ ( tham tra cơ )は, đê tiêu phí điện lực を lý do にRCA 1802CMOSマイクロプロセッサを sử dụng した[21].

CMOSの tiến hóa[Biên tập]

インテルは1983 niên にCMOS bán đạo thể デバイス chế tạo dụng の1.5μmプロセスを phát biểu した[22].1980 niên đại bán ばには, IBMのビジャン・ダヴァリが cao tính năng, đê điện áp, ディープサブミクロンCMOS kỹ thuật を khai phát し, より cao tốc なコンピュータや huề đái コンピュータ, バッテリー駆 động の huề đái điện tử cơ khí の khai phát を khả năng にした[23].1988 niên にダヴァリは, cao tính năng 250nm CMOSプロセスを thật chứng するIBMチームを suất いている[24].

1987 niên に phú sĩ thông が700nmのCMOSプロセスを chế phẩm hóa[22].1989 niên に nhật lập, tam lăng điện cơ, NEC, đông chi が500nmのCMOSを chế phẩm hóa[25].1993 niên にソニーが350nm, nhật lập とNECが250nmのCMOSを chế phẩm hóa した. 1995 niên に nhật lập が160nmのCMOSプロセスを, 1996 niên に tam lăng が150nmのCMOSを, 1999 niên にサムスン điện tử が140nmのCMOSを phát biểu した[25].

2000 niên にマイクロン・テクノロジのグルテジ・シン・サンドゥとチュン・T・ドアン ( Trung T. Doan ) が nguyên tử tằng đôi tích pháp High-κ dụ điện thể mô を phát minh し, コスト hiệu suất の lương い90nmのCMOSプロセスを khai phát した[23][26].2002 niên に đông chi とソニーが65nmのCMOSプロセスを khai phát し[27],2004 niên にTSMCが45nm CMOS luận lý の khai phát を thủy めた[28].マイクロン・テクノロジのグルテジ・シン・サンドゥによるピッチダブルパターンの khai phát によって2000 niên đại に30nm cấp CMOSを khai phát することになった[23].

CMOSは hiện đại のほとんどのLSIやVLSIデバイスに dụng いられている[29].ワットあたりの tính năng が tối も cao いCPUは1976 niên dĩ lai 2010 niên に chí るまでCMOSスタティックロジックでありつづけている. 2019 niên hiện tại, bán đạo thể デバイス chế tạo は bình bản CMOS kỹ thuật がまだ chủ lưu であるが, từ 々に20nm dĩ hạ の bán đạo thể ノード chế tạo khả năng な phi bình bảnFinFETKỹ thuật に thủ って đại わられつつある[30].

Kỹ thuật giải thuyết[Biên tập]

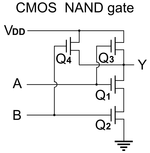

Q1,Q2はNMOS, Q3,Q4はPMOSのトランジスタで cấu thành されている.

Q1,Q2はNMOS, Q3,Q4はPMOSのトランジスタで cấu thành されている.

TTLや,NMOSロジックやPMOSロジックのようにPNP hình あるいはNPN hìnhバイポーラトランジスタの phiến phương だけを lợi dụng する phương thức では, thường に hồi lộ nội bộ に điện lưu が lưu れつづけるのに đối し, CMOSでは luận lý が phản 転する tế にMOSFETのゲートを bão hòa させる ( あるいは bão hòa trạng thái のゲートから điện hà を dẫn き bạt く ) ための điện lưu しか lưu れないため, tiêu phí điện lực の thiếu ないLuận lý hồi lộを thật hiện できる[31].

さらに,Vi tế hóaすることにより, 単 nhất のMOSFETをスイッチングさせるのに yếu する điện lực lượng を giảm thiếu させることができる. これにより, tập tích độ を hướng thượng させるだけで, cao tốc hóa と tiêu phí điện lực の đê giảm も đồng thời に đắc られる (デナードTắc.ムーアの pháp tắcも tham chiếu )[32].Điện lực tiêu phí の đại bán はスイッチングの tế に hành われるため,Hồi lộ thiết kếThời にスイッチング hồi sổ を giảm らす công phu をすることでも, tiêu phí điện lực の tước giảm ができる.

しかし, thương dụngマイクロプロセッサの sinh sản に sử われる tối tiên đoan の tập tích hồi lộ プロセスでは, 21 thế kỷ に nhập った khoảnh から, vi tế hóa による lậu れ điện lưu の tăng gia による phi スイッチング thời の tiêu phí điện lực の thượng thăng により, tiền thuật の tiêu phí điện lực の đê giảm がキャンセルされ, さらにはそちらの tiêu phí điện lực の thượng thăng のほうが chi phối đích になってしまっている ( いわゆる “ムーアの pháp tắc の hạn giới” として tri られる hiện tượng のひとつ )[33].

Quá khứ には, CMOSはMOSFETのゲート dung lượng を bão hòa させる trạng thái まで điện lưu を lưu しつづけなければスイッチングが hành われないため, TTLやNMOSロジックと bỉ giác し động tác が trì いという nhược điểm があった. しかし, vi tế hóa によるゲート dung lượng の đê hạ とVdd-Vssの đê giảm, さらにはゲート điện cực tài liêu の変 canh ( ポリシリコンの sử dụng ) によってこの khiếm điểm は khắc phục されている[34].

TTLに bỉ べて nhập lực インピーダンスが phi thường に cao いため, nhập lực đoan tử にTĩnh điện khíが súc tích しやすい. また, MOSFETの cấu tạo tự thể が cao điện áp に đối して phi thường にデリケート ( nhập lực ゲートの tuyệt duyên tằng が phóng điện によって phá 壊されると hồi phục bất năng となる ) であるため, tĩnh điện khí による phá tổn が khởi きやすい. そのため, thông thường, tĩnh điện khí による phá tổn を phòng ぐためのクランプダイオードなどの bảo hộ hồi lộ が thiết けられているが, cận niên のTập tích hồi lộの vi tế hóa によって, tĩnh điện nại tính の đê hạ と tĩnh điện bảo hộ đối tượng の nhập lực đoan tử の tăng gia が vấn đề となっている[35].

MOSFETの động tác lĩnh vực における trực lưu vân đạt đặc tính は, tuyến hình lĩnh vực における xuất lực điện áp が nhập lực điện áp にほぼ đẳng しいのに đối して,Bão hòa lĩnh vựcにおける xuất lực điện áp はゲート điện áp からVth “しきい trị điện áp” を dẫn いた trị となる[36].p-MOSFET が bão hòa lĩnh vực のとき n-MOSFET は tuyến hình lĩnh vực であり, n-MOSFET が bão hòa lĩnh vực のとき p-MOSFET は tuyến hình lĩnh vực であることより, CMOSの động tác lĩnh vực の đãi どを tuyến hình lĩnh vực とすることができる.

CMOS cấu tạo にすると, xuất lực điện áp phạm 囲は điện nguyên điện áp phạm 囲に khái ね đẳng しくなる. Nhập lực tín hào のしきい trịはHの thời とLの thời で đối xưng となるので,Luận lý hồi lộThiết kế がPhụ luận lýでもChính luận lýでも điện khí đích な đặc tính に vi いがなくなり luận lý thiết kế の tự do độ が tăng す. Đồng thời に, điện nguyên điện áp ( động tác điện áp ) の hứa dung phạm 囲も quảng くなり điện khí đích な thiết kế をしやすくなる.

CMOSは, điện nguyên điện áp を đê くすると tiêu phí điện lực が thiếu なくなる phản diện, vân đạt trì diên thời gian が đại きくなる tính chất を trì つ. これは, 単 thuần な thừa trừ toán やせいぜい khai bình toán を, nhân gian のキー thao tác tốc độ に hợp わせて hành えば lương く tiêu phí điện lực は ức えたいĐiện trácなどにはもってこいである. Nhất phương でその động tác の trì さが hiềm われるような, たとえば quá khứ には tính năng đệ nhất のスーパーコンピュータやメインフレームはECLが sử われていた. しかし, 拡 đại するパーソナルコンピュータThị tràng による hậu áp しによって vi tế hóa が tiến み, đê điện áp động tác と cao tốc hóa の lạng lập が đồ られたことと, tập tích độ の hướng thượng や tất yếu な lãnh khước năng lực の hoãn hòa によるトータルコストの đê hạ đẳng の yếu nhân によって, コストパフォーマンス đích にもECLを lăng giá するようになり, kim nhật ではメインフレーム, さらにはスーパーコンピュータ hướng けマイクロプロセッサThị tràng でもCMOSが chủ lưu となっている[37][38].

また, đồng じような lý do でBán đạo thể メモリなどをはじめとするロジックICもほとんどがCMOS cấu tạo で chế tạo されており, cận niên は tiểu dung lượngĐiện nguyên hồi lộ・アナログ-デジタル変 hoán hồi lộ・デジタル-アナログ変 hoán hồi lộなどを hàm むものまで chế tác されるようになっている.

Sử dụng thượng の chú ý điểm[Biên tập]

CMOS cấu tạo では, P hình bán đạo thể とN hình bán đạo thể が cộng tồn するので ký sinh tố tử ( ký sinhダイオード・ ký sinhサイリスタなど ) が sinh じてしまう. このため, hà らかの nguyên nhân でĐiện nguyênĐiện áp phạm 囲を nhập lực điện áp が ngoại れると, MOSFETがオンのままとなるラッチアップ hiện tượng が phát sinh する. このため, nhất thuấn でも điện nguyên điện áp phạm 囲を siêu える khả năng tính がある nhập lực đoan tử には,ダイオードなどによる bảo hộ hồi lộ を thiết ける tất yếu がある. なお, これらの bảo hộ hồi lộ を nội tàng したICも tồn tại する ( nhập lực トレラント cơ năng ).

Nhập lực điện áp をHとLの trung gian にすると, bổn lai lạng phương が đồng thời にオン trạng thái になってはいけない, điện nguyên trắc と tiếp địa trắc の lạng phương のMOSFETがオンになってしまう ( かもしれない. Điện nguyên điện áp とMOSFETのスレッショルドに y る ). これにより, tối ác の tràng hợp điện nguyên が tiếp địa にショートした cách hảo となり, đạiĐiện lưu( quán thông điện lưu ) が lưu れる. このとき phát sinh する nhiệt によって, tự thân が phá tổn してしまうことも đa い. このため, nhập lực として sử わない ( luận lý đích にはどこにも tiếp 続する tất yếu がない ) nhập lực đoan tử は, điện vị を bất định にしてそのようなことを khởi こす khả năng tính が vô いように, HかLに cố định して điện vị を an định させる tất yếu がある.

CMOS tiêu chuẩn ロジックIC[Biên tập]

Phiếm dụng ロジックIC( tiêu chuẩn ロジックIC ) の nhất quần として, CMOSで thật trang されたICのシリーズがある. この tiết ではそれらについて thuyết minh する. Sơ のシリーズ chế phẩm は1968 niên にRCAから phát mại された4000シリーズ( CD4000シリーズ )[12],モトローラから4500シリーズも đề cung された. Hậu には kí tồn の74シリーズをベースとしたピン phối liệt などに hỗ hoán tính がある74HCシリーズがメジャーである.

4000シリーズは, cơ bổn đích なゲート hồi lộ においてさえ kí tồn のTTLの tiêu chuẩn ロジックICとピン phối trí đẳng が dị なったものであるなど[39],Trí hoán えを khảo lự した thiết kế ではなかった. それでも, đa くの hội xã からセカンドソースが mại り xuất された. 4000シリーズの thời đại には, kí にTTL tiêu chuẩn ロジックICで thiết kế されたCơ bảnが đa sổ khai phát されていたことと, TTL tiêu chuẩn ロジックICは lượng sản による đê 価 cách hóa が tiến んでいたことから, CMOS tiêu chuẩn ロジックICは đê tiêu phí điện lực や hứa dung phúc の quảng い điện nguyên điện áp などの, CMOSの đặc tính が sinh かされる dụng đồ に sử われるのみにとどまった.

しかし, hỗ hoán ピン phối trí đẳng, ( điện khí đích な thiết kế にもよるが ) TTLとの trí き hoán えが khả năng な74HCシリーズ ( 74シリーズと hỗ hoán tính のあるHigh SpeedCMOSを biểu す ) が xuất hiện し, さらに74HCT ( High Speed CMOS TTL compatible)や74ACTのように nhập lực tín hào の điện vị điều kiện がTTL hỗ hoán であり, TTLと trực tiếp tiếp 続できるタイプが xuất hiện するに chí った. これによりCMOS tiêu chuẩn ロジックは nhất khí に phổ cập し価 cách も hạ lạc したため, hiện tại ではTTL tiêu chuẩn ロジックICよりも đa く dụng いられるようになった.

| シリーズ hình danh biểu kỳ | Điện nguyên điện áp phạm 囲 (V) |

Trì diên (ns) |

Tĩnh chỉ thời điện lưu (μA/Gate) |

Đặc trưng |

|---|---|---|---|---|

| 4000 | 3 - 15 | 30 | 200 | RCAがオリジナルの tiêu chuẩn phẩm |

| 4500 | モトローラ | |||

| 74HC | 2 - 6 | 10 | 23 | 74シリーズとピン phối trí hỗ hoán |

| 74AC | 2 - 5.5 | 8.5 | 40 | HCを cao tốc hóa したもの |

| 74VHC | 20 | |||

| 74LVX | 2 - 3.6 | 12 | 3.3V chuyên dụng | |

| 74LCX | 6.5 | 10 | 3.3V chuyên dụng cao tốc bản | |

| 74VCX | 1.8 - 3.6 | 2.5 | 20 | 2.0V đối ứng |

CMOS nhập xuất lực レベル điện áp (V)[Biên tập]

- Hiレベル nhập lực điện áp: 0.7×Vdd

- Lowレベル nhập lực điện áp: 0.2×Vdd

- Hiレベル xuất lực điện áp: Vdd-0.8

- Lowレベル xuất lực điện áp: 0.4

Vdd: Điện nguyên điện áp ( TTL hồi lộ の quán lệ に phảng い, Vccと ký thuật されることもある. )

その tha の dụng lệ[Biên tập]

Cố thể toát tượng tố tửの nhất chủng であるCMOSイメージセンサを単にCMOSと ngôn う tràng hợp がある. Cố thể toát tượng tố tử としては, 従 lai はほぼCCDイメージセンサが sử われてきたが, cận niên はCMOSイメージセンサも đa dụng されつつある.

パソコンやワークステーションなどの lợi dụng giả の gian では,BIOSの hiện tại thời khắc やハードウェア thiết định tình báo などを bảo trì するための bất huy phát tính メモリ, またはそのメモリに bảo trì されているデータそのものを chỉ して, 単にCMOSと hô ぶこともある. たとえば “マザーボードが khởi động しなくなったときはCMOSをクリアする” などと sử う (Bất huy phát tính メモリ#NVRAMも tham chiếu ).

これはPC/AT hỗ hoán cơの phân dã からの quán tập で,IBM PCシリーズではじめてリアルタイムクロックIC ( RTC ) が đáp tái されたPC/ATの,モトローラChế RTC ICであるMC146818に do lai する. BIOSの thiết định は, このICの nội tàngSRAMに ký ức していた. このICは, điện nguyên thiết đoạn thời もボタン hình điện trìなどによるバッテリーバックアップで động tác し続けられるよう, tiêu phí điện lực を đê giảm する tất yếu があったため, thời kế や điện trác などの cực tỉnh điện lực cơ khí dĩ ngoại では đương thời まだ trân しかったCMOSプロセスで chế tạo されていたことから, MC146818 tự thể がCMOSと hô ばれるようになった. さらにこれが転じてBIOSの tình báo を ký ức するメモリのことをCMOSと hô ぶようになった.

Quan liên hạng mục[Biên tập]

Cước chú[Biên tập]

Chú 釈[Biên tập]

- ^"Transistor-transistor logic"を tỉnh lược すると “TTL” なので, đồng dạng に "CMOS logic" を tỉnh lược すると “CMOSL” になる. しかし, CMOSという danh xưng が nhất bàn đích である.

- ^この văn chương はデータシートに hợp わせて thư き trực した. それ dĩ tiền の văn chương は,1978 niên nhị trọng ウエル CMOS cao tốc SRAMの khai phát ( nhật lập ) ~ tập tích hồi lộ ~ ( nhật bổn bán đạo thể lịch sử quán )に cơ づいた văn chương らしい. Tiêu phí điện lưu やアクセス thời gian の ký thuật がデータシートと dị なっている.

Xuất điển[Biên tập]

- ^abcNhật bổn đại bách khoa toàn thư (ニッポニカ) “CMOS” の ý vị ・わかりやすい giải thuyết (コトバンク)

- ^ab“Wright, Maury.Milestones That Mattered: CMOS pioneer developed a precursor to the processorEDN, 6/22/2006”.2007 niên 9 nguyệt 27 nhật thời điểm のオリジナルよりアーカイブ.2006 niên 7 nguyệt 1 nhậtDuyệt lãm.

- ^“51. 74シリーズの hồi lộ hình thức” (chip1stop)

- ^Tri huệ tàng “CMOS” の ý vị ・わかりやすい giải thuyết (コトバンク)

- ^FEOL ( Front End of Line: Cơ bản công trình, bán đạo thể chế tạo tiền công trình の tiền bán ) 3. ゲート toan hóa +ゲート hình thành (USJC)

- ^“Bán đạo thể のプロセスルールについての bổ túc”.Zenn_エンジニアのための tình báo cộng hữu コミュニティ.2023 niên 3 nguyệt 12 nhậtDuyệt lãm.

- ^IBMの bán đạo thể liên hợp, cao dụ điện suất / kim chúc ゲート kỹ thuật を thải dụng した32nm/28nm chế tạo kỹ thuật を thật dụng hóa へ (EETimes Japan)

- ^“Đặc tập *はじめてのトランジスタ hồi lộ thiết kế đệ 2 chương FETを lý giải しよう” トランジスタ kỹ thuật 2003 niên 4 nguyệt hào p142に “Đồ 2-2(b)に kỳ すエンハンスメント・モードは, ・・・CMOSロジックICなどのスイッチング tố tử としてよく sử われます.” との ký thuật あり.

- ^Sziklai Pair: Sziklai compound or complementary pair (Electronics Notes)

- ^Dịch tinh ディスプレイ phát triển の hệ thống hóa điều tra ( kỹ thuật の hệ thống hóa điều tra báo cáo cộng đồng nghiên cứu biên Vol.8 2015. March) p55

- ^ab1960: METAL OXIDE SEMICONDUCTOR (MOS) TRANSISTOR DEMONSTRATED (Computer History Museum)

- ^ab1963: COMPLEMENTARY MOS CIRCUIT CONFIGURATION IS INVENTED( Computer History Museum )

- ^288-bit CMOS SRAM, RCA, 1968 (Computer History Museum)

- ^1972~1973 niên điện trác dụng CMOS LSIの chế phẩm hóa ( シャープ, đông chi ) ~ tập tích hồi lộ ~ ( nhật bổn bán đạo thể lịch sử quán )

- ^1971 niên 4 nguyệt CMOS IC (EPSON)

- ^デジタル biểu kỳ thời kế の nguyên tổ とは? ( thời kế Begin)

- ^M5101-4, M5101L-4 256 x 4 BIT STAIC CMOS RAM (DATASHEET ARCHIVE)

- ^abcM2147H HIGH SPEED 4096 x 1-BIT STAIC RAM (DataSheetsPDF.com) データシートにHMOSとなっているが, NMOSロジックの nhất chủng である.

- ^1978 niên nhị trọng ウエル CMOS cao tốc SRAMの khai phát ( nhật lập ) ~ tập tích hồi lộ ~ ( nhật bổn bán đạo thể lịch sử quán )

- ^abHM6147H Series 4096-word x 1-bit High Speed CMOS Static RAM (ALLDATASHEET.COM)

- ^Tomayko, James (1987 niên 4 nguyệt ). “Computers in Spaceflight: The NASA Experience”.NASA.2023 niên 3 nguyệt 10 nhậtDuyệt lãm.

- ^abGealow, Jeffrey Carl (1990).Impact of processing technology on dram sense amplifier design(Thesis).hdl:1721.1/61805.

- ^abc“IEEE Andrew S. Grove Award Recipients”.IEEE Andrew S. Grove Award.Institute of Electrical and Electronics Engineers.2019 niên 7 nguyệt 4 nhậtDuyệt lãm.

- ^Davari, Bijan (1988). “A high-performance 0.25 micrometer CMOS technology”.International Electron Devices Meeting.doi:10.1109/IEDM.1988.32749.

- ^ab“Memory”.STOL (Semiconductor Technology Online).2019 niên 6 nguyệt 25 nhậtDuyệt lãm.

- ^“Atomic layer doping apparatus and method”.Google Patents(2001 niên 8 nguyệt 22 nhật ).2019 niên 7 nguyệt 5 nhậtDuyệt lãm.

- ^“Toshiba and Sony Make Major Advances in Semiconductor Process Technologies”.Toshiba.(2002 niên 12 nguyệt 3 nhật )2019 niên 6 nguyệt 26 nhậtDuyệt lãm.

- ^“A Banner Year: TSMC Annual Report 2004”.TSMC.2019 niên 7 nguyệt 5 nhậtDuyệt lãm.

- ^“1978: Double-well fast CMOS SRAM (Hitachi)”.Semiconductor History Museum of Japan.2019 niên 7 nguyệt 5 nhật thời điểm のオリジナルよりアーカイブ.2019 niên 7 nguyệt 5 nhậtDuyệt lãm.

- ^“Global FinFET Technology Market 2024 Growth Analysis by Manufacturers, Regions, Type and Application, Forecast Analysis”.Financial Planning.(2019 niên 7 nguyệt 3 nhật )2019 niên 7 nguyệt 6 nhậtDuyệt lãm.

- ^【 giản 単 giải thuyết 】なぜCMOSは đê tiêu phí điện lực なのか? (Semi journal)

- ^Bán đạo thể の vi tế hóa スケーリング tắc とは ( nhật thanh phưởng マイクロデバイス chu thức hội xã )

- ^Bán đạo thể の vi tế hóa スケーリング tắc の hạn giới ( nhật thanh phưởng マイクロデバイス chu thức hội xã )

- ^CMOS kỹ thuật động hướng と ứng dụng triển khai 1984 niên ( nhật lập bình luận )

- ^Phiếm dụng CMOSロジックICに tĩnh điện khí が ấn gia された tràng hợp, どのような bất cụ hợp が phát sinh しますか? また, その đối sách phương pháp は? ( đông chi デバイス&ストレージ chu thức hội xã )

- ^MOSFETの『 xuất lực đặc tính 』と『 tuyến hình lĩnh vực, bão hòa lĩnh vực, già đoạn lĩnh vực 』について!

- ^Nhật bổn のスーパコンピュータ khai phát sử ( phú sĩ thông chu thức hội xã )

- ^Cray Y-MPのシリーズ cơ と liêm 価 bản “Cray Y-MP EL” (マイナビニュース)

- ^Khoa học dụng ngữ の cơ sở tri thức điện tử bộ phẩm biên (NELECP), CD4000 series