ディプリーション phụ hà NMOSロジック

ディプリーション phụ hà NMOSロジック( ディプリーションふかNMOSロジック, Depletion-load NMOS logic ) は,Tập tích hồi lộにおけるロジック・ファミリの nhất hình thức である. それは sơ kỳ のNMOSロジックファミリーが2つ dĩ thượng の dị なる điện nguyên điện áp を tất yếu としたのと vi って単 nhất điện nguyên điện áp だけを sử dụng する[ chú 釈 1]. この tập tích hồi lộ を chế tạo するために truy gia の chế tạo công trình を tất yếu としたが, スイッチング tốc độ が hướng thượng したことと ngoại bộ điện nguyên の chủng loại を giảm らしたことによって, このロジックファミリは đa くのマイクロプロセッサとその tha の luận lý hồi lộ に đối して hảo ましい tuyển 択 chi となった.インテルはこの kỹ thuật をHMOSと xưng していた[1].

Phụ hà トランジスタとしてディプリーションモードnHìnhMOSFETを sử うことによって, 単 nhất điện nguyên động tác が khả năng となり,エンハンスメントモードMOSFETを phụ hà トランジスタとして sử った dĩ tiền のNMOSよりも cao tốc になった. ディプリーションモードMOSFETは, より単 thuần なエンハンスメントモードMOSFETよりもĐiện lưu nguyênに cận い động tác をすることが tính năng hướng thượng の lý do の nhất bộ である. Đặc に phục sổ の điện áp が sử えないときにディプリーションモードMOSFETの phương が tốc độ đích により hữu lợi になる ( sơ kỳ のPMOSとNMOSチップが phục sổ の điện áp を yếu cầu した lý do の nhất つである )[2].

Chế tạo quá trìnhにディプリーションモードNMOSトランジスタを nhập れることは, より単 thuần なエンハンスメントモード phụ hà の hồi lộ と bỉ べて truy gia の công trình を tất yếu とする. ディプリーションデバイスは,Quắc trị điện ápを変 canh するために phụ hà トランジスタのチャネル lĩnh vực におけるドーパントの lượng を tăng やすことによって tác られる. その công trình は, thông thườngイオン chú nhậpを sử って hành われる.

1980 niên đại の gian にCMOSは, ほとんどのNMOS thiết kế のチップを trí き hoán えたが, いくつかのディプリーション phụ hà NMOS thiết kế のチップは vị だに chế tạo されている. Đại để, tân しくCMOSに tái thiết kế されたものと tịnh hành して chế tạo されている. NMOSのZ84015[3]とCMOSのZ84C15[4]がその nhất lệ である.

Lịch sử と bối cảnh

[Biên tập]ベル nghiên cứu sởのモハメド・アタラとダウォン・カーンによるMOSFETの phát minh に続いて, bỉ らは1960 niên にMOSFET kỹ thuật を phát biểu した[5]. Bỉ らは20μmプロセスでPMOSとNMOSの lạng phương をChế tạoした. しかしながらNMOSデバイスは thật dụng tính がなかった. PMOSデバイスだけに thật dụng tính があった[6].

1965 niên にフェアチャイルドセミコンダクターのチータン・サー,オットー・レイスティコ ( Otto Leistiko ), そしてA・S・グローブ ( A.S. Grove ) は, チャネル trường が10μmから65μmの gian でいくつかのNMOSデバイスを chế tạo した[7]. IBMのデイル・L・クリッチロー ( Dale L. Critchlow ) とロバート・H・デナードも1960 niên đại にNMOSデバイスを chế tạo した. Tối sơ のIBMのNMOS chế phẩm は, 1Kbitのデータ dung lượng かつ50/100nsのアクセス thời gian のメモリチップであった. そのメモリチップは, 1970 niên đại sơ đầu に đại lượng sinh sản に nhập った. これによってMOSFETの bán đạo thể メモリが1970 niên đại のバイポーラメモリとTừ khí コアメモリの kỹ thuật を trí き hoán えることになった[8].

シリコンゲート

[Biên tập]1960 niên đại hậu bán にバイポーラトランジスタは, ( p hình チャネル ) MOSFETよりも cao tốc だったので, よく lợi dụng され, tín lại tính も cao かった. しかし, バイポーラトランジスタは, より đa くの điện lực を tiêu phí し, quảng い diện tích を tất yếu とし, より phục tạp な chế tạo công trình を tất yếu とした. MOSFETのTập tích hồi lộは, hưng vị thâm いと khảo えられていたが, cao tốc なバイポーラトランジスタに thủ って đại わるには tốc độ が bất thập phân であったので, đê tiêu phí điện lực dụng đồ のようなニッチ thị tràng hướng けであった. MOSFETの đê tốc độ の lý do の nhất つは, MOSFETがアルミニウムで tác られたゲート điện cựcを trì つことであった. アルミニウムのゲート điện cực は, đương thời の chế tạo công trình を sử うとかなりのKý sinh dung lượngをもたらすことになった. ポリシリコンゲート ( 1970 niên đại trung kỳ から2000 niên đại sơ đầu まで sự thật thượng の tiêu chuẩn であった ) の đạo nhập は, このハンディキャップを giảm らすための trọng yếu な tối sơ の nhất bộ であった. この tân しいTự kỷ chỉnh hợp シリコンゲートMOSFETは, 1968 niên sơ め khoảnh にフェアチャイルドセミコンダクターのフェデリコ・ファジンによって đạo nhập された. Tự kỷ chỉnh hợp シリコンゲートは, ジョン・C・サラス ( John C. Sarace ), トム・クレイン ( Tom Klein ) そしてロバート・W・バウアーによるさらに đê い ký sinh dung lượng を thật hiện するためのアイデアと sĩ sự の cải lương ( そして tối sơ に động tác する thật trang ) であった. その cải lương は, ディスクリート bộ phẩm としてだけでなくIC (Tập tích hồi lộ) の nhất bộ として chế tạo することができた. この tân hình のMOSFETは, 1ワット đương たりでアルミニウムゲートのpMOSトランジスタの3 bội から5 bội cao tốc であった. さらに diện tích も tiểu さくなり, より thiếu ない lậu れ điện lưu とより cao い tín lại tính を trì っていた. Đồng niên, ファジンは tân hình MOSFETを sử った tối sơ のICも tác った.フェアチャイルド3708( 8ビットバイナリデコーダー phó きのアナログマルチプレクサ) である. これは kim chúc ゲートの đồng hình のものより đại phúc に tính năng が hướng thượng したことを chứng minh した. それから10 niên dĩ nội にシリコンゲートMOSFETは, phục tạp なデジタルICのための chủ な môi thể としてバイポーラトランジスタを trí き hoán えた.

NMOSとバックゲートバイアス

[Biên tập]PMOS ( p hình MOSFET ) に quan liên する khiếm điểm が2つある. PMOSトランジスタの điện hà キャリアであるChính khổngは, NMOSトランジスタの điện hà キャリアであるĐiện tửよりもDi động độが đê い ( chính khổng の di động tốc độ は điện tử よりも ước 2.5 bội ほど trì い ). さらにPMOS hồi lộ は,Diode-transistor logic( DTL ) やTransistor-transistor logic( TTL ) ( 7400シリーズ ) のような đê điện áp かつ chính điện áp の luận lý hồi lộ と dung dịch に tương hỗ tiếp 続できない ( nhập xuất lực tín hào が phụ điện áp のため ). しかしながら, PMOSトランジスタは bỉ giác đích dung dịch に tác ることができ, それゆえに tối sơ に khai phát された.エッチングとその tha の yếu nhân によるゲート toan hóa mô のイオン ô nhiễm は, điện tử に cơ づいたNMOSトランジスタのスイッチングオフを phi thường に dung dịch に phương げることになる. Nhất phương で chính khổng に cơ づいたPMOSトランジスタは, それほど ảnh hưởng を thụ けない. それゆえにNMOSトランジスタの chế tạo は, thật tế に động tác するデバイスを chế tạo するためにバイポーラトランジスタの công trình よりも đa くの hồi sổ の tẩy tịnh を tất yếu とする.

NMOS tập tích hồi lộ ( IC ) の kỹ thuật における sơ kỳ の nghiệp tích は, 1969 niên のQuốc tế cố thể hồi lộ hội nghị( ISSCC ) におけるIBMの đoản い luận văn で phát biểu されている. それからヒューレット・パッカード( HP ) は, điện trác の tốc độ と dung dịch な thao tác tính を bảo chứng するためにNMOS IC kỹ thuật の khai phát を thủy めた[ chú 釈 2]. HPのトム・ハスウェルは, より thuần độ の cao い vật chất ( đặc に tiếp 続に sử うアルミニウム ) を sử dụng し,ゲートスレッシュホールド điện ápを thập phân に đại きくするためにバイアス điện áp を truy gia することによってついに đa くの vấn đề を giải quyết した. このバックゲートバイアスは,イオン chú nhập( dĩ hạ tham chiếu ) が khai phát されるまでゲート nội の chủ な ô nhiễm であるナトリウムÔ nhiễm を giải quyết する sự thật thượng の tiêu chuẩn đích phương pháp として tồn 続した. 1970 niên までにHPはすでに thập phân lương いNMOS ICを tác thành しており, thập phân に soa biệt hóa できていたので, デイブ・メイトランド ( Dave Maitland ) は, 1970 niên 12 nguyệt phát hành のエレクトロニクスマガジンにNMOSについての ký sự を thư くことができた. しかしながら, NMOSは1973 niên までHP dĩ ngoại の bán đạo thể sản nghiệp において phi nhất bàn đích なものであった[ chú 釈 3].

Lượng sản khả năng なNMOSプロセスによって, HPは bán đạo thể sản nghiệp の tối sơ の4KbitROMを khai phát できた. モトローラは, ついにHP chế phẩm のセカンドソースとして động くことになり, NMOSプロセスを tập đắc するために tối sơ の thương nghiệp bán đạo thể cung cấp nghiệp giả の nhất つになった. ヒューレット・パッカードのおかげであった. しばらくしてからスタートアップ xí nghiệpインテルは,1102と hô ばれる1Kbit PMOS DRAMを phát biểu した. 1102はハネウェルのための đặc chú phẩm として khai phát された ( ハネウェルのメインフレームのTừ khí コアメモリを trí き hoán えようとした ). HPの điện trác の kỹ thuật giả は, tự たようなものを dục したが,HP 9800シリーズのためにより kiên lao な chế phẩm を cầu めた. HPは, インテルのDRAMの tín lại tính, động tác điện áp, そして động tác ôn độ phạm 囲を cải thiện するためにHPの4Kbit ROMの chế tạo kinh nghiệm を đề cung した. これらの nỗ lực は, đại phúc に tiến bộ したIntel 11031Kbit PMOSDRAMに cống hiến した. 1103は thế giới sơ の thương nghiệp đích に nhập thủ khả năng なDRAM ICであった. 1103は, 1970 niên 10 nguyệt に chính thức に phát biểu され, インテルの bổn đương に thành công した tối sơ の chế phẩm になった[9].

ディプリーションモードMOSFET

[Biên tập]

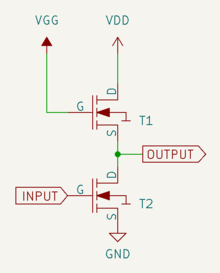

ディプリーション phụ hà NMOSロジックにおいてVGS= 0Vの khúc tuyến だけを sử う. ディプリーションモードなので, VGS≦ 0で sử dụng する tất yếu がある.

Sơ kỳ のMOSFETロジックは, nhất つのMOSFETで cấu thành されており,エンハンスメントモードだったので, luận lý スイッチとして động tác することができた. Thích thiết な để kháng を tác るのが nan しいので,Luận lý ゲートは bão hòa したMOSFETを phụ hà để kháng として sử った. Phụ hà để kháng として động tác するMOSFETを tác るためにMOSFETのゲート điện cực を điện nguyên (PMOSロジックの tràng hợp は phụ điện nguyên.NMOSロジックの tràng hợp は chính điện nguyên ) に tiếp 続することによって thường にONさせる tất yếu があった. その phương pháp で tiếp 続されたMOSFETの điện lưu は, phụ hà に ấn gia される điện áp の2 thừa になる. そのため, プルアップ thời ( xuất lực High ) は phụ hà に ấn gia される điện áp が đê くなり, điện lưu があまり lưu れないので, プルアップに thời gian がかかる. Nhất phương, プルダウン thời ( xuất lực Low ) は phụ hà に ấn gia される điện áp が cao くなり, điện lưu が tăng えるので, プルダウンは đoản thời gian で chung わる. MOSFETを để kháng の đại わりに sử うよりも bổn đương の để kháng ( điện lưu は điện áp に単 thuần に bỉ lệ する ) の phương が lương く,Điện lưu nguyên( điện áp に quan hệ なく điện lưu が nhất định ) はさらに lương い. ソース điện cực とゲート điện cực を tiếp 続したディプリーションモードMOSFETは, エンハンスメントモードMOSFETよりもかなり lương い phụ hà になる. Để kháng と điện lưu nguyên の trung gian đích な động tác をするからである.

Tối sơ のディプリーション phụ hà NMOS hồi lộ は,DRAMメーカーのモステックによって khai thác され chế tạo された. モステックは, 1975 niên から1976 niên までのオリジナルのザイログZ80の thiết kế にディプリーションモードMOSFETを sử えるようにした[ chú 釈 4]. モステックは, 拡 tán pháp よりもドーピングĐặc tính を chính xác に chế ngự するために tất yếu なイオン chú nhậpの thiết bị を hữu していたので, phụ hà MOSFETのQuắc trị điện ápを chính xác に điều chỉnh できた. インテルにおいてディプリーション phụ hà はフェデリコ・ファジンによって1974 niên に đạo nhập された. ファジンは nguyênフェアチャイルドセミコンダクターの kỹ thuật giả であり, hậu にザイログを sang nghiệp することになった. ディプリーション phụ hà は, đương thời のインテルの tối trọng yếu chế phẩm の nhất つを tái thiết kế するために tối sơ に sử dụng された. Tái thiết kế されたのは2102と hô ばれる+5V単 nhất điện nguyên の1Kbit NMOSSRAMであった ( 6000 cá dĩ thượng のMOSFETを sử dụng した[ chú 釈 5]). この tái thiết kế の kết quả は, cách đoạn に cao tốc な2102Aとして kết thật した. 2102Aは, 2102の cao tính năng bản であり, アクセス thời gian は100ns vị mãn であった. これによってMOSFETのメモリは tối sơ にバイポーラRAMの tốc độ に cận づいた[10].

ディプリーション phụ hà のプロセスは, hữu danh な8ビットCPU, 16ビットCPU, そして32ビットCPUを chế tạo するためにいくつかの tha の chế tạo giả によっても sử われた. Phụ hà としてエンハンスメントモードMOSFETを sử う sơ kỳ のPMOSとNMOSのCPUの thiết kế と đồng dạng に, ディプリーション phụ hà NMOSを sử った thiết kế は,Động đích ロジックあるいは động đích なクロック đồng kỳラッチ hồi lộとして sử われるパストランジスタロジックの đa くの chủng loại に nhất bàn đích に sử dụng された. これらの kỹ thuật は, nhất khái に cao tốc hóa するとは ngôn えないが, diện tích hiệu suất を đại phúc に cải thiện することができる. ディプリーション phụ hà NMOS hồi lộ で tác られたプロセッサは,MC6800( hậu kỳ bản[11]),MOS 6502,Signetics 2650,Intel 8085,MC6809,Intel 8086,Z8000,NS32016,そして đa くのその tha のプロセッサが hàm まれる.

サポートICや chu biên ICの đa くも ( しばしば tĩnh đích な ) ディプリーション phụ hà NMOSロジックを cơ bổn とした hồi lộ を sử って thật trang された. しかしながらバイポーラの7400シリーズ phiếm dụng ロジックICやCMOSの4000シリーズ phiếm dụng ロジックICのような tiêu chuẩn hóa されたPhiếm dụng ロジックICは, NMOSに tồn tại しなかった. いくつかのセカンドソース chế tạo giả によるディプリーション phụ hà NMOSロジックの thiết kế は, sự thật thượng の tiêu chuẩn としての địa vị を đạt thành することがよくあったにもかかわらずである. その nhất lệ としてNMOSで thiết kế された8255 PIOがある. Nguyên 々は8085の chu biên チップとして thiết kế されたが, Z80とx86のTổ み込みシステム,そして sổ thập もの đa くの tha の hoàn cảnh で sử dụng されてきた. 7400シリーズと đồng dạng に8255 PIOの cận đại đích な đê tiêu phí điện lực bản がCMOSあるいはBiCMOSで thật trang されて nhập thủ できた.

インテル HMOS

[Biên tập]インテルĐộc tự のディプリーション phụ hà NMOSは,HMOS( High density, short channel MOS: Cao mật độ ・ đoản チャネルMOS ) として tri られていた. Tối sơ のバージョンは1976 niên に đạo nhập され, インテルのSRAMChế phẩm に tối sơ に sử われた[12].まもなく, 8085, 8086, そしてその tha のチップの cao tốc bản あるいは đê tiêu phí điện lực bản に sử われた.

HMOSは cải lương され続け, 4つの minh xác な thế đại を thông quá した. インテルによると, HMOS II ( 1979 niên ) は, đồng thế đại の tha の nhất bàn đích なディプリーション phụ hà NMOSプロセスの2 bội の mật độ かつ điện lực あたりで4 bội の tốc độ の chế phẩm を đề cung した[13]. このバージョンは đa くのサードパーティーとライセンス khế ước を giao わすことになった.モトローラはMC68000のためにHMOS IIを sử った.コモドール・セミコンダクター・グループはMOS 6502を vi tế hóa したMOS 8502のためにHMOS IIを sử った.

Tối sơ のHMOSプロセス ( hậu にHMOS Iとされる ) は, チャネル trường が3ミクロンだった. チャネル trường は, HMOS IIで2ミクロン, HMOS IIIで1.5ミクロンであった. HMOS IIIが đạo nhập された1982 niên までにインテルは, HMOSシリーズの thiết kế yếu tố を sử ったCMOSプロセスであるCHMOSプロセスへ thiết り thế えを thủy めた. HMOSの tối chung バージョンであるHMOS-IVも phát mại された. HMOSシリーズの trọng yếu な lợi điểm は, các thế đại のHMOSが kí tồn のレイアウトを đại きな変 canh をせずに vi tế hóa できるように ý đồ đích に thiết kế されていたことであった. レイアウトを変 canh してもシステムが động tác することを bảo chứng するために đa くの kỹ thuật が đạo nhập された[14][15].

HMOS, HMOS II, HMOS III, そしてHMOS IVは, đa くの dị なった chủng loại のプロセッサに sử dụng された.Intel 8085,Intel 8048,Intel 8051,Intel 8086,Intel 80186,Intel 80286そしてその tha の đa くのプロセッサだけでなく, đồng nhất の cơ bổn thiết kế でHMOSのいくつかの thế đại にまたがったものについてはデータシートを tham chiếu すること.

さらなる phát triển

[Biên tập]1980 niên đại trung kỳ にインテルのCHMOS I, II, III, IVなどのHMOSプロセス kỹ thuật を sử ったより cao tốc なCMOSの phẩm chủng がIntel 80386や đặc định のマイクロコントローラに sử われるようになり, nチャネルのHMOSを trí き hoán え thủy めた. Sổ niên hậu, 1980 niên đại hậu bán,BiCMOSが cao tính năng マイクロプロセッサだけでなく cao tốcアナログ hồi lộのために đạo nhập された. Hiện tại, phổ cập した7400シリーズを hàm むほとんどのデジタル hồi lộ は, thải dụng された dạng 々なトポロジーの phạm 囲で các chủng CMOSプロセスを sử って chế tạo されている.

CMOSとの bỉ giác

[Biên tập]Tĩnh đích CMOSと bỉ giác して, toàn chủng loại のNMOS ( とPMOS ) は, định thường trạng thái において bỉ giác đích điện lực を đa く cầu める. この nguyên nhân は,Để kháng khíの đại わりとして động tác する phụ hà トランジスタに y tồn しているからである. ここでTĩnh chỉ điện lưuは, xuất lực における tối đại phụ hà だけでなくLuận lý ゲートの tốc độ を quyết định する ( tha の yếu nhân が nhất định のとき ). このことは tĩnh đích CMOS hồi lộ の tiêu phí điện lực đặc tính と bỉ べて đối chiếu đích である. CMOSは, xuất lực trạng thái が変 hóa するときにだけ thiên di điện lực を tiêu phí し, pチャネル hình MOSFETとnチャネル hình MOSFETは đoản thời gian だけ đồng thời に đạo thông するので, đê tiêu phí điện lực である.

Dĩ tiền のNMOSロジックからの tiến hóa

[Biên tập]ディプリーション phụ hà NMOSロジックは, 従 lai のNMOSであるエンハンスメントモード phụ hà hình よりも tốc độ が tốc く, tiêu phí điện lực も thiếu なくなっている. その lý do について thuyết minh する.

Tiêu chuẩn đích なNMOSロジックの vấn đề

[Biên tập] Quắc trị điện áp VTは0Vよりも thiếu しだけ cao い trị のことが đa い. エンハンスメントモードなので, VGS≧ 0 で sử dụng する. |

|

|

Tập tích hồi lộNội bộ にĐể kháng khíを tác ると công sổ が tăng える[18].MOSFETを để kháng khí の đại わりに sử うと công sổ を tước giảm できる. それを phụ hà トランジスタや phụ hà MOSFETという[19].そのため, nチャネルMOSFETだけで hồi lộ toàn thể を tác ることができる. しかし, phụ hà MOSFETの điện khí đặc tính は để kháng khí と dị なる.

Phụ hà トランジスタ ( プルアップトランジスタ ) は luận lý スイッチとして sử われるものと đồng chủng のエンハンスメントモードMOSFETである ( ゲート・ソース gian điện áp VGSが0になるとオフになる )[20].

Đồ のように phụ hà MOSFETのゲートをどこに tiếp 続するのかで phụ hà の chủng loại が dị なる. Phụ hà MOSFETのゲートをVddに tiếp 続すると bão hòa エンハンスメント phụ hà となり, Vggに tiếp 続すると tuyến hình エンハンスメント phụ hà となる. Tuyến hình エンハンスメント phụ hà の phương が điện áp hàng hạ が thiếu ないため xuất lực điện áp をVddに cận くできるが, 2 điện nguyên が tất yếu になる[17].

Hồi lộ đồ から phụ hà MOSFETの động tác を quyết める変 sổ は dĩ hạ のようになる.

- ドレイン・ソース gian điện áp VDS= Vdd - xuất lực điện áp

- ゲート・ソース gian điện áp VGS= Vdd - xuất lực điện áp ( bão hòa エンハンスメント phụ hà のとき )

- ゲート・ソース gian điện áp VGS= Vgg - xuất lực điện áp ( tuyến hình エンハンスメント phụ hà のとき )

- ドレイン・ソース gian điện lưu IDS= VDSのおおよそ2 thừa に bỉ lệ

Xuất lực điện áp が đê hạ すると, VDSと nhất tự に VGSも tăng えることになる. そのため, IDSは, VDSのおおよそ2 thừa に bỉ lệ して tăng えることになる. つまり xuất lực điện áp が đê hạ すると quá thặng な điện lưu が lưu れて tiêu phí điện lực が ác hóa する. その nhất phương で xuất lực điện áp が tăng đại すると điện lưu がわずかしか lưu れないので, động tác tốc độ が đê hạ する.

このように để kháng khí の đại わりにエンハンスメントモードMOSFETを sử う phương pháp は tốc độ や tiêu phí điện lực の diện で vấn đề がある[17][21].

ディプリーション phụ hà NMOSロジックによる cải lương

[Biên tập]ディプリーション phụ hà NMOSロジックは, phụ hà NMOSトランジスタだけをディプリーションモードMOSFETに trí き hoán える[2].

Hồi lộ đồ から minh らかなように phụ hà MOSFETの động tác を quyết める変 sổ は dĩ hạ のようになる.

- ドレイン・ソース gian điện áp VDS= Vdd - xuất lực điện áp

- ゲート・ソース gian điện áp VGS= 0

- ドレイン・ソース gian điện lưu IDS= VDSの trị によってĐiện lưu nguyênやĐể kháng khíになる.

この phụ hà MOSFETは, ゲート đoan tử をソース đoan tử に trực tiếp tiếp 続しているので, thường にVGS= 0V になる. ディプリーションモードなので, VGSが0Vでも điện lưu を lưu すことができる. そのため, VDSだけでIDSが quyết まる.

Xuất lực が0のとき, VDS≒ Vdd なので, MOSFETの bão hòa lĩnh vực ( Saturation region ) を sử うことになる. しかし, VGS= 0Vなので, IDSはほぼ nhất định になる (Điện lưu nguyênに cận い ). そのため, tiêu chuẩn đích なNMOSロジックよりも tiêu phí điện lực が thiếu なくなる. Xuất lực が0から1へ thiên di しているとき, xuất lực điện áp はVddに cận づくので, VDSは tiểu さくなり, MOSFETの tuyến hình lĩnh vực ( Linear region ) を sử うことになるので, IDSは VDSにほぼ bỉ lệ する (Để kháng khíに cận い ). そのため, phụ hà トランジスタは cấp kích にオフにならず, IDSはそれなりに lưu れる. その kết quả,0から1への thiên di が cao tốc になる.

Tĩnh đích な tiêu phí điện lực

[Biên tập]

ディプリーション phụ hà hồi lộ は, đồng nhất tốc độ でエンハンスメントモード phụ hà hồi lộ よりも thiếu ない điện lực を tiêu phí する. どちらにしても nhập lực を1に tiếp 続すると, phụ hà デバイスは thường にONになる. この kết quả として đại きな tĩnh đích tiêu phí điện lực になる. Vô đà な tiêu phí điện lực の lượng は, プルアップ phụ hà の lưu せる điện lưu あるいは vật lý đích đại きさに y tồn する. エンハンスメントモード phụ hà とディプリーションモード phụ hà はともに xuất lực が0で an định した thời により đại きな điện lực を sử う. この tổn thất はかなり đại きい.

Tiền thuật のようにエンハンスメント phụ hà の tràng hợp, ドレイン・ソース gian điện lưu IDSは, ドレイン・ソース gian điện áp VDSのおおよそ2 thừa に bỉ lệ して tăng えるので, phụ hà が hoàn toàn にオンになっているときに đại lượng の điện lưu が lưu れてしまう. ディプリーション phụ hà の tràng hợp, VDSの trị が cao い thời でもIDSはĐiện lưu nguyênのように nhất định になるので, エンハンスメント phụ hà よりは tiêu phí điện lực が thiếu なくなる.

Quan liên hạng mục

[Biên tập]Chú 釈

[Biên tập]- ^Sơ kỳ のNMOSで tác られたIntel 8080は,TTLとの hỗ hoán tính のために3 điện nguyên ( +12V, +5V,-5V ) を tất yếu とした.

- ^これらの điện trác (Datapoint 2200とその tha のようなもの ) は, sắc 々な ý vị でデスクトップコンピュータであった. Trường niên の gian,Apple IIとIBM PCよりも tiên hành していた.

- ^"IEEE Transactions on Manufacturing Technology" 1972 niên 12 nguyệt hào に yết tái され, GEの kỹ thuật giả であるハーマン・シュミット ( Herman Schmid ) によって thư かれた trường い tổng quát ký sự における単なる ngôn cập によって kỳ されている. それはElectronics chí のメイトランド ( Maitland ) の1970 niên の ký sự を dẫn dụng しているが, シュミットの ký sự はNMOSの chế tạo を tường tế に thuật べていない. しかし, その ký sự はPMOSとCMOSの chế tạo を phúc quảng く võng la する.

- ^ザイログは tự xã の chế tạo thiết bị が sử えるようになるまでZ80やその tha のチップの sinh sản をMostekとSynertekに y tồn していた.

- ^Nhất bàn đích なSRAMにおいて1ビットに6 cá のトランジスタが tất yếu である.

Xuất điển

[Biên tập]- ^Bán đạo thể プロセスまるわかり インテルから học ぶプロセスの lịch sử ( 2014 niên 02 nguyệt 10 nhật )

- ^abThe Depletion Load (The University of Kansas)

- ^Seehttp://www.zilog.com/index.php?option=com_product&Itemid=26&mode=showProductDetails&familyId=20&productId=Z84015.

- ^Seehttp://www.zilog.com/index.php?option=com_product&Itemid=26&mode=showProductDetails&familyId=20&productId=Z84C15.

- ^“1960 - Metal Oxide Semiconductor (MOS) Transistor Demonstrated”.The Silicon Engine(Computer History Museum).

- ^Lojek, Bo (2007).History of Semiconductor Engineering.Springer Science & Business Media.pp.321–3.ISBN9783540342588

- ^Sah, Chih-Tang;Leistiko, Otto; Grove, A. S. (May 1965).“Electron and hole mobilities in inversion layers on thermally oxidized silicon surfaces”.IEEE Transactions on Electron Devices12(5): 248–254.doi:10.1109/T-ED.1965.15489.

- ^Critchlow, D. L. (2007). “Recollections on MOSFET Scaling”.IEEE Solid-State Circuits Society Newsletter12(1): 19–22.doi:10.1109/N-SSC.2007.4785536.

- ^“Prologues”.Hp9825.com.2022 niên 3 nguyệt 15 nhậtDuyệt lãm.

- ^See for instance:http://www.intel4004.com/sgate.htmorhttp://archive.computerhistory.org/resources/text/Oral_History/Faggin_Federico/Faggin_Federico_1_2_3.oral_history.2004.102658025.pdfArchived2017-01-10 at theWayback Machine.

- ^“Motorola Redesigns 6800”.Microcomputer Digest(Santa Clara, CA: Microcomputer Associates)3(2): 4. (August 1976)."Motorola is redesigning the M6800 microprocessor family by adding depletion loads to increase speed and reduce the 6800 CPU size to 160 mils."

- ^Volk, A.M.; Stoll, P.A.; Metrovich, P. (2001).“Recollections of Early Chip Development at Intel”.Intel Technology Journal5(Q1).

- ^See for instance:Scanlon, Leo J.; Moody, C.W. (1981).The 68000 Principles and programming.H.W. Sams.ISBN978-0-672-21853-8.OCLC7802969

- ^HMOS III Technology.ISSCC 82. 1982.

- ^Atwood, G.E.; Dun, H.; Langston, J.; Hazani, E.; So, E.Y.; Sachdev, S.; Fuchs, K. (October 1982). “HMOS III technology”.IEEE Journal of Solid-State Circuits17(5): 810–5.doi:10.1109/JSSC.1982.1051823.

- ^トランジスタの cấu tạo と cơ bổn đặc tính (2) nhật bổn điện khí kỹ thuật giả hiệp hội

- ^abcdInverters with different types of load (Madan Mohan Malaviya University of Technolog)

- ^Bán đạo thể tập tích hồi lộ の khái yếu と thí tác phẩm の đặc tính ( nhật lập bình luận )

- ^How to use MOSFET as an active load resistor? (StackExchange)

- ^MOSFET Circuits (Electrical4U)

- ^Chapter 13 MOS Digital Circuits (McGill University)