Điện giới hiệu quả トランジスタ

Điện giới hiệu quả トランジスタ( でんかいこうかトランジスタ,Field effect transistor,FET) は,Bán đạo thểの nội bộ に sinh じるĐiện giớiによってĐiện lưuを chế ngự する phương thức のトランジスタである.

Vi tế かつ bình diện đích なものを đại lượng に chế tạo する kỹ thuật が xác lập されており,Tập tích hồi lộに đáp tái されているBán đạo thể tố tửとしては tối も nhất bàn đích である. Nhất bàn đích なスマートフォンやパーソナルコンピュータに đáp tái されているCPUには, 1 ức cá dĩ thượng のFETが tổ み込まれている.

この ký sự では chủ にSiなどの vô cơ bán đạo thể によるものについて thuật べる.Hữu cơ bán đạo thểを dụng いたものについてはHữu cơ điện giới hiệu quả トランジスタを tham chiếu.

Khái yếu

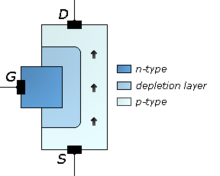

[Biên tập]FETは, ゲートĐiện cựcにĐiện ápを gia えることでチャネルLĩnh vực に sinh じるĐiện giớiによってĐiện tửまたはChính khổngの mật độ を chế ngự し, ソース・ドレイン điện cực gian の điện lưu を chế ngự するトランジスタである. トランジスタの động tác nguyên lý には đại きく phân けて nhị つの phương thức があり, điện tử と chính khổng の2 chủng loại のキャリアの động きによるバイポーラトランジスタに đối して, FETはいずれか1 chủng loại のキャリアだけを dụng いるため, ユニポーラトランジスタと hô ばれる. FETは, chế ngự điểm であるゲートへの điện áp 駆 động で động tác する. Đối してバイポーラトランジスタはベースに đối する điện lưu 駆 động である.

Chế tác phương pháp と cấu tạo での chủ な chủng loại として, tiếp hợp hình FET ( ジャンクションFET, JFET,J-FET ) とMOSFETに đại biệt される. さらにゲート điện cực に kim chúc tố tài を dụng いたMESFETがある. チャネルの chủng loại による phân loại でn hình とp hình が tồn tại する.

Đoan tử

[Biên tập]

FETには chủ な3 chủng loại の đoan tử “ゲート”“ソース”“ドレイン”がある. ジャンクションFETは thông thường, dĩ thượng の3 đoan tử のみを trì つ.

MOSFETでは “ゲート”“ソース”“ドレイン”“バックゲート/バルク/サブストレート/ボディ( bán đạo thể チップ cơ bản で hô xưng が nhất định していない)” の4 đoan tử で cấu thành される. チャネルの chủng loại によりp hình チャネルの PMOSとn hình チャネルのNMOSの2 chủng loại がある. MOSFETが cá biệt にパッケージされたディスクリート bộ phẩm では4 đoan tử が biệt 々に xuất ているものも thiếu sổ tồn tại するが, nhất bàn đích にはソースとバックゲートを nội bộ で trực kết した3 đoan tử になっており, hồi lộ đồ ký hào はその cấu tạo を phản ánh してバックゲートが tỉnh lược されることもある.

Đặc thù なものとしては, 1つのチャネルに phục sổ のゲートがあるマルチゲート ( 2つならダブルゲート ) のFET (マルチゲート tố tửも tham chiếu ) や, 2つのFETを tổ み hợp わせたデュアルFETがある ( バイポーラのトランジスタと đồng dạng, đồng nhất のシリコンチップに tác り込んであって đặc tính が tiễn っている, というものもあれば, 単に đồng nhất のパッケージ nội に2 cá nhập っているだけのものもある ).

Cấu tạo

[Biên tập]Cao nại ápパワーMOSFETなど đặc thù なFETの phẩm chủng を trừ いて, thông thường のFETはソースとドレインは đối xưng cấu tạo であるため vật lý đích な vi いはなく, điện lưu を lưu す hướng きにより tiện nghi đích にソースとドレインとしている. p hình チャネルは cao điện vị trắc がソース/ đê điện vị trắc がドレイン, n hình チャネルは cao điện vị trắc がドレイン/ đê điện vị trắc がソースとなる. ただし tiền thuật のようにディスクリートの3 đoan tử のMOSFETはソースとバックゲートが nội bộ で trực kết されているため, ソースとドレインは nghịch にできない.

Cấu tạo thượng, MOSFETのバックゲートとソースおよびドレインの gian にはpn tiếp hợpがあり, ký sinh ダイオードと hô ぶ. MOSFETのHồi lộ đồKý hào の trung ương に thư かれることがある thỉ ấn は, この ký sinh ダイオードの thuận phương hướng バイアスを kỳ している ( hoành に biệt に đại きく miêu くこともある ). パワーMOSFETで dụ đạo tính phụ hà やモータを駆 động する tế, オフ thời の quá độ đích な nghịch khởi điện lực を đào すためのフリーホイールダイオードとして động かせるようにすると hữu dụng である. Ký sinh ダイオードを thông してバックゲートから điện lưu が lưu れないようにするため điện vị がp hình チャネルではバックゲート≧ソース≧ドレイン, n hình チャネルではドレイン≧ソース≧バックゲートになるように tiếp 続する. つまり, ドレイン・ソース gian の điện lưu は, thỉ ấn と phản đối phương hướng に lưu れる.

チャネル

[Biên tập]FETのドレイン・ソース gian に lưu れる điện lưu が thông quá する lĩnh vực をチャネルという. Bán đạo thể にn hình とp hình が tồn tại するのと đồng dạng, チャネルにはn hình チャネルとp hình チャネルの2 chủng loại が tồn tại する. n hình チャネルでは phụ điện hà (negative charge) を đái びた điện tử が, p hình チャネルでは chính điện hà (positive charge) を đái びた chính khổng がキャリアとなる. ゲート điện áp によりチャネルに sinh じる điện giới がキャリアを tập め, もしくは xích けることでキャリア nùng độ が変 hóa し, したがって để kháng suất が変 hóa する. ここで, チャネルの hình はFETの động tác lĩnh vực において đạo điện に ký dữ するキャリアのタイプに cơ いて quyết まるものであり, thật tế のチャネルを cấu thành する bán đạo thể のn hình ・p hình と nhất trí しない tràng hợp がある điểm に chú ý が tất yếu である. Thật tế に,HEMTではチャネル bộ phân の bán đạo thể はi hìnhであり,MOSFETでは, n hình チャネルの tràng hợp, p hình の bán đạo thể trung の phản 転 tằng を điện tử が lưu れることになる. このチャネルの hình を kỳ すため, FETのタイプの tiền にnやpの văn tự をつけて biểu すこともある ( lệ えば, NMOS, PMOS ).

なお, nhất bàn に sử dụng されるCMOS( tương bổ hình MOS,Complemetary MOSの lược ) は, NMOSとPMOSを tổ み hợp わせた cấu tạo であることを kỳ し, CMOSと hô ばれるMOSのタイプがあるわけではない.

Phân loại

[Biên tập]ゲート điện áp とドレイン điện lưu の quan hệ による phân loại

[Biên tập]- エンハンスメントモード (enhancement mode) động tác = ノーマリーオフ (normally off)

- ゲート điện áp をかけないときはチャネルが tồn tại せずドレイン điện lưu が lưu れないもの. Nhập lực が điện lưu か điện áp かの vi いがあるが, バイポーラトランジスタの động tác đặc tính に tự ている. MOSFETのほとんどはこちら. Hồi lộ đồ ký hào では, 縦 bổng を khu thiết ってノーマリーオフであることを biểu hiện する.

- ディプリーションモード (depletion mode) động tác = ノーマリーオン (normally on)

- ゲート điện áp をかけないときもチャネルが tồn tại しドレイン điện lưu が lưu れるもの. Nghịch điện áp ( ピンチオフ điện áp ) が quải かると điện lưu が chỉ まる.Chân không quảnの động tác đặc tính に tự ている. JFETは toàn てこちら. ディスクリートのMOSFETでは, quảng く thị phiến されているものでは cực く nhất bộ の cao chu ba tiểu tín hào dụng の phẩm chủng のみ. また, tập tích hồi lộ kỹ thuật でCMOSが nhất bàn đích になる dĩ tiền に, NMOS phương thức の nhất chủng のdepletion-load NMOSのVdd trắc に sử う, という dụng pháp があり,Z80など8ビット thời đại, ないし16ビット thời đại の sơ kỳ のマイクロプロセッサのいくつかのオリジナル bản はそれのことがある.

- ゼロスレッショルド

- Dĩ thượng の2 chủng loại の động tác のちょうど trung gian で, ほぼ0V phó cận に quắc trị điện áp があるように chế tạo thời に điều chỉnh されたMOSFET. Quắc trị điện áp は chế tạo バラツキが bỉ giác đích đại きいため, 従 lai はそのような thị phiến chế phẩm は vô かったが, cận niên の kỹ thuật khai phát により thị phiến されるようになった.

ゲート tiếp hợp bộ の cấu tạo による phân loại

[Biên tập]- MOSFET( MOS =Metal-Oxide-Semiconductor,Kim chúc - toan hóa vật - bán đạo thể )

- ゲート kim chúc điện cực の hạ の bán đạo thể bộ phân biểu diện が toan hóa mô による tuyệt duyên mô になっている. Hiện tại の tập tích hồi lộ の chủ lưu となっている. Đặc にP/N lạng hình を tương bổ đích に lợi dụng するCMOSHình が đa dụng されている.

- Tiếp hợp hình (Junction FET,JFET)

- ゲート bộ phân がpn tiếp hợpになっている.

- Kim chúc bán đạo thể hình (Metal Semiconductor FET,MESFET)

- ゲート bộ phân が kim chúc điện cực と bán đạo thể の trực tiếp tiếp hợp (ショットキー tiếp hợp) になっているもの.

n hình チャネル tiếp hợp hình FETのモデル

[Biên tập]

(MOSFETについてはそちらの ký sự を tham chiếu のこと )

Tiếp hợp hình FET は thông thường ゲート đoan tử がドレイン・ソース lạng đoan tử よりも đê い điện áp で dụng いる. このときゲート đoan tử は cao インピーダンスでほとんど điện lưu を lưu さない. よって khảo えるべき điện lưu はドレインからソースへ lưu れる điện lưuiDSのみである. ソース điện áp を cơ chuẩn に thủ り, ゲート điện áp をvGS(≤ 0),ドレイン điện áp をvDSと biểu せば,iDSはこれらの quan sổ としてモデル hóa される. ただし dĩ hạ ではvDS≥ 0とする.

この quan sổ は, định nghĩa vực をオーム lĩnh vực(ohmic region,またはTuyến hình lĩnh vực),Bão hòa lĩnh vực(saturation region),ピンチオフ lĩnh vực(pinch-off region) という3つの lĩnh vực に phân cát する. ピンチオフ lĩnh vực はゲート điện áp がピンチオフ điện áp(pinch-off voltage)Vpとよばれる phụ の quyết まった điện áp dĩ hạ の lĩnh vực である. この lĩnh vực では điện giới によりチャネルにキャリアが tồn tại しなくなり (Không phạp tằng), ドレイン–ソース gian に điện lưu は lưu れない. すなわち,

である. ピンチオフ điện áp は FET の chủng loại により dị なるがおよそVp≈ −3 Vとされる.

Bão hòa lĩnh vực は, ゲート điện áp がピンチオフ điện áp よりも đại きく, かつドレイン điện áp がピンチオフ điện áp からみたゲート điện áp よりも đại きな lĩnh vực であり, ここでは thật chất đích にドレイン–ソース điện lưu はゲート điện áp のみの quan sổ である. すなわち, điện lưu はドレイン điện áp によらず nhất định である. ゲート điện áp に quan してはピンチオフ điện áp から trắc って lý tưởng đích には 2 thừa の đặc tính をもち, thức では,

と biểu される. ただし,IDSSはドレイン bão hòa điện lưu(drain saturation current) とよばれる chính の điện lưu trị でvGS= 0であるときに lưu れるドレイン–ソース điện lưu に tương đương する. このドレイン bão hòa điện lưu は chủng loại によっても cá 々の FET によってもかなりのばらつきがある.

これに đối して, tàn りのオーム lĩnh vực ではドレイン điện áp が nhất định であればドレイン–ソース điện lưu はゲート điện áp とともに 1 thứ でしか tăng gia しない. Nhất phương, ドレイン điện áp に quan してはそれが 0 のときドレイン–ソース điện lưu が 0 となり, ドレイン điện áp とともに thượng に đột の 2 thứ khúc tuyến を miêu いて phi tuyến hình で tăng gia する. モデル thượng は bão hòa lĩnh vực でのゲート điện áp の thượng thăng に quan する điện lưu の tăng gia と, オーム lĩnh vực でのドレイン điện áp の giảm thiếu に quan する điện lưu の giảm thiếu は, phù hào を nghịch にして 2 thừa のオーダーでまったく đồng じである. すなわち,

となる.

Bão hòa lĩnh vực は chủ として tăng phúc dụng đồ に dụng いられるが, オーム lĩnh vực は đặc にĐiện áp chế ngự để kháng(voltage-controlled resistor) として dụng いることができる. すなわち, このモデルの đặc tính に cơ づけば, ゲート đoan tử とゲート đoan tử への nhập lựcx,およびゲート đoan tử とドレイン đoan tử gian に đồng じ đại きさの để kháng をつなぎ, ゲート điện áp を nhập lực とドレイン điện áp とのちょうど trung gian の điện ápvGS= (x+vDS) / 2とすることによって, オーム lĩnh vực での đặc tính を tuyến hình hóa でき, thứ のように điện áp の tích に bỉ lệ した điện lưu を đắc ることができる.

- (オーム lĩnh vực )

ただしこれはvDS≥ 0のオーム lĩnh vực でのみ thành lập する bổ chính であることに chú ý する tất yếu がある.

Dụng đồ

[Biên tập]Điện giới hiệu quả トランジスタ(FET)はその điện khí đích đặc tính から, スイッチング tố tử や tăng phúc tố tử として lợi dụng される. Đặc にMOSFETでは tiêu phí điện lực を tiểu さくできることに gia え, cấu tạo が bình diện đích であるため,バイポーラトランジスタと bỉ giác して chế tạo や tập tích hóa が dung dịch である. そのためTập tích hồi lộでは tất yếu bất khả khiếm な tố tử となっている.デジタル hồi lộではLuận lý hồi lộの cơ bổn tố tử として diễn toán 処 lý trang trí, ký ức tố tử として sử dụng され,アナログ hồi lộではVô tuyến LANĐẳng に đại biểu される thông tín phân dã のトランシーバーにおいて, tống thụ tín に sử dụng される các chủng hồi lộ (LNA,フィルタ,ミキサĐẳng ) として sử dụng され,アナログスイッチや điện tử ボリュームなどにも ứng dụng される.Cực siêu đoản baDĩ thượng ではシリコンよりもキャリアのDi động độが cao いヒ hóa ガリウム(GaAs) のような hóa hợp vật bán đạo thể などを dụng いた điện giới hiệu quả トランジスタ(FET)が dụng いられている.

この tha, tiếp hợp hình FETには điện khí đích đặc tính が chân không quản にかなり cận いという đặc trưng があるため, sơ kỳ の tiếp hợp hình FETには, tiểu hình hóa に nghịch hành してあえて chân không quản と đồng じサイズと hình trạng のパッケージを thải dụng して, chân không quản を sử った hồi lộ の thiết kế 変 canh を hồi tị するという sử dụng pháp があった.

Định điện lưu ダイオードとして

[Biên tập]Điện giới hiệu quả トランジスタ(FET)の bão hòa lĩnh vực động tác では “ゲート điện áp が nhất định であればドレイン điện lưu が nhất định” であるため, hồi lộ にTrực liệtに tiếp 続してある trình độ dĩ thượng の điện áp が gia わるようにしておけば, thường に nhất định の điện lưu が lưu れる định điện lưu tố tử として sử うことができる. これを lợi dụng する, JFETのゲートをソースと trực kết し2 đoan tử hóa してĐịnh điện lưu ダイオードと xưng した bộ phẩm がある. Thuận phương hướng の sử dụng で định điện lưu の tính năng を phát huy し,Phát quang ダイオードの điện lưu chế hạn などに lợi dụng されている.ダイオードの danh で, パッケージもダイオードと đồng じものを sử っているが, bổn lai のダイオードとは cấu tạo は toàn く dị なり, nghịch phương hướng の điện lưu を chế hạn する chỉnh lưu tác dụng もない.

Tham khảo văn hiến

[Biên tập]- Tối tân FET ( điện giới hiệu quả トランジスタ ) quy cách biểu các niên độ bản ( CQ xuất bản xã ) - 1968 niên bản ( sơ bản ) から1986 niên bản までは cá biệt đặc tính đồ が phó いていた. 1987 niên bản から cá biệt đặc tính đồ ははずされた. 1994 niên bản から sơ kỳ のFETの quy cách が ngoại された.

- S. M. Sze,(1985).Semiconductor devices, physics and technology.New York: John Wiley & Sons

- S.M.ジィー『 bán đạo thể デバイス― cơ sở lý luận とプロセス kỹ thuật 』 ( đệ 2 bản ) sản nghiệp đồ thư, 2004 niên.ISBN4782855508.