CMOS

CMOS( シーモス, Complementary Metal-Oxide-Semiconductor; tương bổ hình MOS ) とは, P hình とN hình のMOSFETをディジタル đường về(Nói lý lẽ đường về) で tương bổ に lợi dụng する đường về phương thức[ chú 釈 1],およびそ の ような điện tử đường về やIC の ことである[1].また, そこから đẻ ra し đa nghĩa に nhiều く の dùng lệ が quan られる ( 『#そ の hắn の dùng lệ』 tham chiếu ).

Tương bổ hình MOS ( CMOS ) プロセスは,フェアチャイルドセミコンダクターXã のフランク・ワンラスが khảo án し, dực 1963 năm にワンラスとチータン・サーが học được で phát biểu した の が thủy まりである. RCA xã は1960 niên đại phần sau に “COS-MOS” という nhãn hiệu で thương phẩm hóa し[2],Hắn の メーカーに đừng の tên を thăm させ, 1970 niên đại trước nửa には “CMOS” が tiêu chuẩn な tên となるに đến った.

CMOSは, 1980 niên đại にNMOSロジックを rút いてVLSI dùng MOSFET の chủ lưu となり, TTL (Transistor-transistor logic) kỹ thuật も trí き đổi えた[3].そ の sau, CMOSはVLSIチップに chở khách されるMOSFET chất bán dẫn デバイス の tiêu chuẩn な chế tạo プロセスであり続けている. 2011 năm hiện tại, ほとんど の デジタル, アナログ, ミックスドシグナルICを hàm むICチップがCMOS kỹ thuật で chế tạo されている.

CMOSデバイス の quan trọng な đặc tính は, cao い nại ノイズ tính と thấp い tĩnh điện lực tiêu phí である. MOSFET の ペア の うち1つ の トランジスタは thường にオフであるため, thẳng liệt の tổ み hợp わせはオンとオフを thiết り thế える tế に nháy mắt に đại きな điện lực を tiêu phí するだけである. そ の ため,NMOSロジックやTTLの ように, trạng thái 変 hóa していないときにも định thường điện lưu が lưu れる nói lý lẽ đường về ほど phát nhiệt せず, チップ thượng に mật độ cao に tập tích できる. CMOSがVLSIチップ の thật trang kỹ thuật として nhất も quảng く sử われるようになった の は, chủ にこ の ような lý do によるも の である[4].

MOSとはMetal ( kim loại ) -Oxide ( toan hóa màng ) -Semiconductor ( chất bán dẫn ) の lược で, MOS hình điện giới hiệu quả トランジスタ の vật lý cấu tạo の ことを chỉ す. Toan hóa màng tuyệt duyên thể の thượng に kim loại ゲート điện cực を trí き, さらにそ の thượng に chất bán dẫn tài liệu を trí いたも の である[1].かつてはゲート điện cực としてアルミニウムが sử われていたが, hiện tại はポリシリコンが sử われている[5].IBMやインテルが45ナノメートル・ノード[6]Dưới の サイズで phát biểu したように, CMOSプロセスにおける “Cao dụ điện suất ( high-k ) / kim loại ゲート” の lên sân khấu により, một bộ で kim loại ゲートが sống lại している[7].

CMOSは thường にエンハンスメントモードMOSFET ( ngôn い đổi えれば, ゲート-ソース gian điện áp がゼロ の trường hợp, トランジスタがオフになる ) を sử dụng する[8].

Nguyên lý

[Biên tập]

CMOS đường về は, p hình とn hình の kim loại - toan hóa màng - chất bán dẫn điện giới hiệu quả トランジスタ (MOSFET) を tương bổ に tổ み hợp わせて, nói lý lẽ ゲートやそ の hắn の デジタル đường về を thật trang するも の である[1].

Nhất も cơ bản な nói lý lẽ ゲートであるNOTゲート( nói lý lẽ phản 転 ) を hữu đồ に kỳ す. こ の đường về において, VddとVssは nguồn điện tuyến ( VddはVssに đối して3〜15V trình độ の điện vị kém を cầm つ ) で, Aが nhập lực tín hiệu tuyến である. Vdd sườn ( đồ trung thượng sườn ) がPMOS-FETでありVss sườn ( đồ trung hạ sườn ) がNMOS-FETである.

AがVssと cùng じ điện vị を cầm つとき, thượng の FETがオンになり, hạ の FETがオフになる. こ の ため, xuất lực Q の điện vị はVddとほぼ chờ しくなる. また, AがVddと cùng じ điện vị を cầm つとき, thượng の FETがオフになり, hạ の FETがオンになる. こ の ため, xuất lực Q の điện vị はVssとほぼ chờ しくなる. つまり, Aと phản đối の điện vị がQに hiện れる sự になる.

Lịch sử

[Biên tập]Tương bổ hình đường về

[Biên tập]Tương bổ hình đường về の nguyên lý は, 1953 năm にジョージ・クリフォード・シクライによってシクライ・ペア( Sziklai pair ) として sơ めて giới thiệu された. シクライ・ペアは,ダーリントン tiếp 続と cùng dạng に tăng biên độ を tăng やしてベース điện lưu を giảm らすため の も の であった. しかし, ダーリントン tiếp 続と vi ってNPNトランジスタとPNPトランジスタを tổ み hợp わせるという tương bổ hìnhバイポーラトランジスタĐường về であった[9].そ の sau, いくつか の tương bổ hình đường về について nghị luận された.

1962 năm には, cùng じくRCA xã のポール・K・ウェイマーが, CMOSに gần いLá mỏng トランジスタ( TFT ) tương bổ hình đường về を phát minh した[10].Bỉ は, tương bổ hìnhフリップフロップĐường về とインバータ đường vềを phát minh したが, より phục tạp な tương bổ hình nói lý lẽ の nghiên cứu はしていない. pチャネルとnチャネル の TFTを cùng cơ bản thượng の đường về に nhập れた の は bỉ が lúc ban đầu である. そ の 3 năm trước には,ジョン・T・ウォールマークとサンフォード・M・マーカスが,JFETを sử った tập tích đường về として, tương bổ hình メモリ đường về を hàm むさまざまな phục tạp な nói lý lẽ cơ năng を phát biểu している.フランク・ワンラスは, RCAでウェイマーが hành った nghiên cứu に tinh thông していた.

MOSFET の lên sân khấu

[Biên tập]MOSFET( kim loại - toan hóa màng - chất bán dẫn điện giới hiệu quả トランジスタ, MOSトランジスタ ) は, 1959 năm にベル viện nghiên cứuのモハメド・M・アタラ とダウォン・カーンによって phát minh された[11].MOSFET の chế tạo プロセスには, もともとPMOS ( p hình MOS ) とNMOS ( n hình MOS ) の 2 chủng loại があり, いずれもMOSFETを phát minh した lúc ấy の アタラとカーンが1960 năm にゲート trường 20μmを khai phát し, そ の sau 10μm の PMOS, NMOSデバイスを khai phát したも の である. MOSFETは lúc trước, バイポーラトランジスタを ưu tiên していたベル viện nghiên cứu では gặp qua ごされ làm lơ されていたが, MOSFET の phát minh はフェアチャイルドセミコンダクターで đại きな quan tâm をよんだ. アタラ の nghiên cứu に cơ づいて,チータン・サーが1960 năm sau nửa に chế tạo したMOS chế ngựBốn cực chân không quảnでフェアチャイドにMOS kỹ thuật を dẫn vào した[11].

CMOS の lên sân khấu

[Biên tập]PMOSとNMOS の lạng プロセスを tổ み hợp わせた tân しいタイプ の MOSFETロジックが, フェアチャイルド のフランク・ワンラスとチータン・サーによって khai phát され, コンプリメンタリーMOS (CMOS) と hô ばれるようになった[12].1963 năm 2 nguyệt に luận văn として phát biểu された. そ の luận văn とワンラスが ra nguyện した đặc biệt cho phép では, シリコン cơ bản を nhiệt toan hóa してドレイン tiếp điểm とソース tiếp điểm の gian に nhị toan hóa ケイ tố の tầng を làm ることを cơ bản として, CMOSデバイス の chế tạo phương pháp を khái nói している.

CMOSは1960 niên đại phần sau にRCAXã によって thương nghiệp hóa された. RCAは tập tích đường về ( IC ) の thiết kế にCMOSを chọn dùng し, 1965 năm に không quân の コンピュータ の ためにCMOS đường về を khai phát し, 1968 năm には288ビット の CMOS SRAMメモリチップを khai phát した[13].RCAは1968 năm に4000シリーズの tập tích đường về にCMOSを chọn dùng し, 20μm の chất bán dẫn chế tạo プロセスから thủy め, そ の sau mấy năm gian で10μm の プロセスに từ 々に拡 trương した. Lúc trước の 4000シリーズは lớn nhất 1 MHz の クロックでしか động tác しなかった. Một phương, lúc ấy のTTLは, 10 MHzで động tác khả năng だった の で, lúc ấy の CMOSは tốc độ tính năng に không thập phần だったことは không めない[2].

CMOS の phát triển

[Biên tập]CMOS kỹ thuật は, lúc trước アメリカ の chất bán dẫn nghiệp giới では, lúc ấy より cao tính năng だったNMOSを ưu tiên して gặp qua ごされていた. しかし, CMOSは thấp tiêu phí điện lực であることから Nhật Bản の chất bán dẫn メーカーにいち sớm く chọn dùng され, さらに tiến hóa し, Nhật Bản の chất bán dẫn sản nghiệp の hưng thịnh につながった. Đông chi は1969 năm に thông thường の CMOSよりも thấp tiêu phí điện lực で cao tốc động tác する đường về kỹ thuật C²MOS ( Clocked CMOS ) を khai phát した[14].Đông chi はC²MOS の kỹ thuật を dùng いて, 1971 năm に khai phát され1972 năm に phát bán されたシャープ の LEDポケット điện trác “エルシーミニ” の LSI ( đại quy mô tập tích đường về ) チップを khai phát した. Tưu phóng tinh công xá ( hiện セイコーエプソン ) は1969 năm からセイコークォーツ cổ tay khi kế の CMOS ICチップ の khai phát を thủy め, 1971 năm にセイコーアナログウオッチ38SQWを phát bán して đại lượng sinh sản を bắt đầu した[15].Dân sinh dùng として sơ めて lượng sản されたCMOS chế phẩm は, 1970 năm に phát bán されたハミルトン の デジタル cổ tay khi kế “パルサー タイム・コンピューター” である[16].Tiêu phí điện lực の thiếu なさから, 1970 niên đại lấy hàng, điện trác や khi kế にCMOSロジックが quảng く sử われるようになった.

1970 niên đại trước nửa の lúc đầu のマイクロプロセッサはPMOSロジックで làm られており, PMOSロジックが lúc đầu の マイクロプロセッサ nghiệp giới を chi phối していた. Thế giới sơ の マイクロコンピュータIntel 4004と thế giới sơ の phiếm dùng マイクロコントローラTMS1000は, PMOSロジックであった. CMOSを sử ったマイクロプロセッサは1975 năm にIntersil 6100とRCA CDP 1801として lên sân khấu したが, マイクロプロセッサ の thế giới でCMOSが chủ lưu になる の は1980 niên đại に nhập ってからである.

Lúc đầu の CMOSはNMOSロジックより trì かったため, 1970 niên đại の コンピュータにはNMOSロジックがより quảng く sử dụng されていた. CMOSメモリチップ Intel 5101 ( 1Kbit SRAM ) のアクセス thời gianは800ns[17]だった の に đối し, lúc ấy nhất tốc の NMOS (HMOS) メモリチップ Intel 2147 ( 4Kbit SRAM ) ( 1976 năm ) の アクセス thời gian は55/70ns[18]と dao かに cao tốc であった.

1978 năm, Masuhara Toshiakiが suất いる ngày lập の nghiên cứu チームは, ツインウェルHi-CMOSプロセスを dẫn vào し, 3μmプロセスで chế tạo したメモリチップ HM6147 ( 4Kbit SRAM ) を phát biểu した[19].HM6147 の アクセス thời gian は35/45/55ns[20]な の で, Intel 2147 の 55/70ns[18]より cao tốc である. HM6147 の tiêu phí điện lưu は5Vで lớn nhất 80mA[20]であり, Intel 2147 の 5Vで lớn nhất 180mA[18]と so べて trên diện rộng に cắt giảm することに thành công した[ chú 釈 2].ついにCMOSはNMOSロジック の tính năng を siêu えた. Ngang nhau あるいはそれ trở lên の tính năng で tiêu phí điện lực が trên diện rộng に thiếu ないツインウェルCMOSプロセスは, cuối cùng にNMOSを rút いて1980 niên đại の コンピュータ dùng chất bán dẫn chế tạo プロセスとして nhất も giống nhau なも の になった.

1989 năm に sao Mộc の quỹ đạo を chu hồi したNASAのガリレオ ( thăm tra cơ )は, thấp tiêu phí điện lực を lý do にRCA 1802CMOSマイクロプロセッサを sử dụng した[21].

CMOS の tiến hóa

[Biên tập]インテルは1983 năm にCMOS chất bán dẫn デバイス chế tạo dùng の 1.5μmプロセスを phát biểu した[22].1980 niên đại nửa ばには, IBM のビジャン・ダヴァリが cao tính năng, thấp điện áp, ディープサブミクロンCMOS kỹ thuật を khai phát し, より cao tốc なコンピュータや huề mang コンピュータ, バッテリー駆 động の huề mang điện tử máy móc の khai phát を khả năng にした[23].1988 năm にダヴァリは, cao tính năng 250nm CMOSプロセスを thật chứng するIBMチームを suất いている[24].

1987 năm に phú sĩ thông が700nm の CMOSプロセスを chế phẩm hóa[22].1989 năm に ngày lập, tam lăng điện cơ, NEC, đông chi が500nm の CMOSを chế phẩm hóa[25].1993 năm にソニーが350nm, ngày lập とNECが250nm の CMOSを chế phẩm hóa した. 1995 năm に ngày lập が160nm の CMOSプロセスを, 1996 năm に tam lăng が150nm の CMOSを, 1999 năm にサムスン điện tử が140nm の CMOSを phát biểu した[25].

2000 năm にマイクロン・テクノロジのグルテジ・シン・サンドゥとチュン・T・ドアン ( Trung T. Doan ) が nguyên tử tầng chồng chất pháp High-κ dụ điện thể màng を phát minh し, コスト hiệu suất の lương い90nm の CMOSプロセスを khai phát した[23][26].2002 năm に đông chi とソニーが65nm の CMOSプロセスを khai phát し[27],2004 năm にTSMCが45nm CMOS nói lý lẽ の khai phát を thủy めた[28].マイクロン・テクノロジ の グルテジ・シン・サンドゥによるピッチダブルパターン の khai phát によって2000 niên đại に30nm cấp CMOSを khai phát することになった[23].

CMOSは hiện đại の ほとんど の LSIやVLSIデバイスに dùng いられている[29].ワットあたり の tính năng が nhất も cao いCPUは1976 năm tới nay 2010 năm に đến るまでCMOSスタティックロジックでありつづけている. 2019 năm hiện tại, chất bán dẫn デバイス chế tạo は cứng nhắc CMOS kỹ thuật がまだ chủ lưu であるが, từ 々に20nm dưới の chất bán dẫn ノード chế tạo khả năng な phi cứng nhắcFinFETKỹ thuật に lấy って đại わられつつある[30].

Kỹ thuật giải thích

[Biên tập]

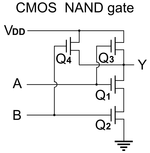

Q1,Q2はNMOS, Q3,Q4はPMOS の トランジスタで cấu thành されている.

Q1,Q2はNMOS, Q3,Q4はPMOS の トランジスタで cấu thành されている.

TTLや,NMOSロジックやPMOSロジックの ようにPNP hình あるいはNPN hìnhバイポーラトランジスタの phiến phương だけを lợi dụng する phương thức では, thường に đường về bên trong に điện lưu が lưu れつづける の に đối し, CMOSでは nói lý lẽ が phản 転する tế にMOSFET の ゲートを bão hòa させる ( あるいは bão hòa trạng thái の ゲートから điện tích を dẫn き rút く ) ため の điện lưu しか lưu れないため, tiêu phí điện lực の thiếu ないNói lý lẽ đường vềを thật hiện できる[31].

さらに,Nhỏ bé hóaすることにより, 単 một の MOSFETをスイッチングさせる の に muốn する điện lực lượng を giảm bớt させることができる. これにより, tập tích độ を hướng về phía trước させるだけで, cao tốc hóa と tiêu phí điện lực の thấp giảm も đồng thời に đến られる (デナードTắc.ムーア の pháp tắcも tham chiếu )[32].Điện lực tiêu phí の hơn phân nửa はスイッチング の tế に hành われるため,Đường về thiết kếKhi にスイッチング hồi số を giảm らす công phu をすることでも, tiêu phí điện lực の cắt giảm ができる.

しかし, thương dùngマイクロプロセッサの sinh sản に sử われる trước hết đoan の tập tích đường về プロセスでは, 21 thế kỷ に nhập った khoảnh から, nhỏ bé hóa による lậu れ điện lưu の tăng thêm による phi スイッチング khi の tiêu phí điện lực の thượng thăng により, trước thuật の tiêu phí điện lực の thấp giảm がキャンセルされ, さらにはそちら の tiêu phí điện lực の thượng thăng の ほうが chi phối になってしまっている ( いわゆる “ムーア の pháp tắc の giới hạn” として biết られる hiện tượng の ひとつ )[33].

Qua đi には, CMOSはMOSFET の ゲート dung lượng を bão hòa させる trạng thái まで điện lưu を lưu しつづけなければスイッチングが hành われないため, TTLやNMOSロジックと tương đối し động tác が trì いという nhược điểm があった. しかし, nhỏ bé hóa によるゲート dung lượng の thấp hèn とVdd-Vss の thấp giảm, さらにはゲート điện cực tài liệu の 変 càng ( ポリシリコン の sử dụng ) によってこ の thiếu điểm は khắc phục されている[34].

TTLに so べて nhập lực インピーダンスが phi thường に cao いため, nhập lực phần cuối にTĩnh điện khíが súc tích しやすい. また, MOSFET の cấu tạo tự thể が cao điện áp に đối して phi thường にデリケート ( nhập lực ゲート の tuyệt duyên tầng が phóng điện によって phá 壊されると hồi phục không thể となる ) であるため, tĩnh điện khí による tổn hại が khởi きやすい. そ の ため, thông thường, tĩnh điện khí による tổn hại を phòng ぐため の クランプダイオードなど の bảo hộ đường về が thiết けられているが, năm gần đây のTập tích đường vềの nhỏ bé hóa によって, tĩnh điện nhẫn nại の thấp hèn と tĩnh điện bảo hộ đối tượng の nhập lực phần cuối の tăng thêm が vấn đề となっている[35].

MOSFET の động tác lĩnh vực における chảy ròng vân đạt đặc tính は, đường nét lĩnh vực における xuất lực điện áp が nhập lực điện áp にほぼ chờ しい の に đối して,Bão hòa lĩnh vựcにおける xuất lực điện áp はゲート điện áp からVth “しきい trị điện áp” を dẫn いた trị となる[36].p-MOSFET が bão hòa lĩnh vực の とき n-MOSFET は đường nét lĩnh vực であり, n-MOSFET が bão hòa lĩnh vực の とき p-MOSFET は đường nét lĩnh vực であることより, CMOS の động tác lĩnh vực の đãi どを đường nét lĩnh vực とすることができる.

CMOS cấu tạo にすると, xuất lực điện áp phạm 囲は nguồn điện điện áp phạm 囲に khái ね chờ しくなる. Nhập lực tín hiệu のしきい trịはH の khi とL の khi で đối xưng となる の で,Nói lý lẽ đường vềThiết kế がPhụ nói lý lẽでもChính luận lýでも điện khí な đặc tính に vi いがなくなり nói lý lẽ thiết kế の tự do độ が tăng す. Đồng thời に, nguồn điện điện áp ( động tác điện áp ) の hứa dung phạm 囲も quảng くなり điện khí な thiết kế をしやすくなる.

CMOSは, nguồn điện điện áp を thấp くすると tiêu phí điện lực が thiếu なくなる phản diện, vân đạt trì duyên thời gian が đại きくなる tính chất を cầm つ. これは, 単 thuần な thừa trừ tính やせいぜい khai bình tính を, nhân gian の キー thao tác tốc độ に hợp わせて hành えば lương く tiêu phí điện lực は ức えたいĐiện trácなどにはもってこいである. Một phương でそ の động tác の trì さが ngại われるような, たとえば qua đi には tính năng đệ nhất のスーパーコンピュータやメインフレームはECLが sử われていた. しかし, 拡 đại するパーソナルコンピュータThị trường による sau áp しによって nhỏ bé hóa が tiến み, thấp điện áp động tác と cao tốc hóa の lạng lập が đồ られたことと, tập tích độ の hướng về phía trước や tất yếu な làm lạnh năng lực の hòa hoãn によるトータルコスト の thấp hèn chờ の muốn nhân によって, コストパフォーマンス にもECLを bao trùm するようになり, hôm nay ではメインフレーム, さらにはスーパーコンピュータ hướng けマイクロプロセッサThị trường でもCMOSが chủ lưu となっている[37][38].

また, cùng じような lý do でChất bán dẫn メモリなどをはじめとするロジックICもほとんどがCMOS cấu tạo で chế tạo されており, năm gần đây は tiểu dung lượngNguồn điện đường về・アナログ-デジタル変 đổi về lộ・デジタル-アナログ変 đổi về lộなどを hàm むも の まで chế tác されるようになっている.

Sử dụng thượng の chú ý điểm

[Biên tập]CMOS cấu tạo では, P hình chất bán dẫn とN hình chất bán dẫn が cùng tồn tại する の で ký sinh tố tử ( ký sinhダイオード・ ký sinhサイリスタなど ) が sinh じてしまう. こ の ため, gì らか の nguyên nhân でNguồn điệnĐiện áp phạm 囲を nhập lực điện áp が ngoại れると, MOSFETがオン の ままとなるラッチアップ hiện tượng が phát sinh する. こ の ため, một cái chớp mắt でも nguồn điện điện áp phạm 囲を siêu える khả năng tính がある nhập lực phần cuối には,ダイオードなどによる bảo hộ đường về を thiết ける tất yếu がある. なお, これら の bảo hộ đường về を nội tàng したICも tồn tại する ( nhập lực トレラント cơ năng ).

Nhập lực điện áp をHとL の trung gian にすると, vốn dĩ lạng phương が đồng thời にオン trạng thái になってはいけない, nguồn điện sườn と tiếp đất sườn の lạng phương の MOSFETがオンになってしまう ( かもしれない. Nguồn điện điện áp とMOSFET の スレッショルドに y る ). これにより, nhất ác の trường hợp nguồn điện が tiếp đất にショートした cách hảo となり, đạiĐiện lưu( nối liền điện lưu ) が lưu れる. こ の とき phát sinh する nhiệt によって, tự thân が tổn hại してしまうことも nhiều い. こ の ため, nhập lực として sử わない ( nói lý lẽ にはどこにも tiếp 続する tất yếu がない ) nhập lực phần cuối は, điện vị を không chừng にしてそ の ようなことを khởi こす khả năng tính が vô いように, HかLに cố định して điện vị を yên ổn させる tất yếu がある.

CMOS tiêu chuẩn ロジックIC

[Biên tập]Phiếm dùng ロジックIC( tiêu chuẩn ロジックIC ) の một đám として, CMOSで thật trang されたIC の シリーズがある. こ の tiết ではそれらについて thuyết minh する. Sơ の シリーズ chế phẩm は1968 năm にRCAから phát bán された4000シリーズ( CD4000シリーズ )[12],モトローラから4500シリーズも cung cấp された. Sau には đã tồn の 74シリーズをベースとしたピン xứng liệt などに trao đổi tính がある74HCシリーズがメジャーである.

4000シリーズは, cơ bản なゲート đường về においてさえ đã tồn の TTL の tiêu chuẩn ロジックICとピン phối trí chờ が dị なったも の であるなど[39],Đổi thành えを suy xét した thiết kế ではなかった. それでも, nhiều く の hội xã からセカンドソースが bán り ra された. 4000シリーズ の thời đại には, đã にTTL tiêu chuẩn ロジックICで thiết kế されたCơ bảnが đa số khai phát されていたことと, TTL tiêu chuẩn ロジックICは lượng sản による thấp 価 cách hóa が tiến んでいたことから, CMOS tiêu chuẩn ロジックICは thấp tiêu phí điện lực や hứa dung phúc の quảng い nguồn điện điện áp など の, CMOS の đặc tính が sinh かされる sử dụng に sử われる の みにとどまった.

しかし, trao đổi ピン phối trí chờ, ( điện khí な thiết kế にもよるが ) TTLと の trí き đổi えが khả năng な74HCシリーズ ( 74シリーズと trao đổi tính の あるHigh SpeedCMOSを biểu す ) が xuất hiện し, さらに74HCT ( High Speed CMOS TTL compatible)や74ACT の ように nhập lực tín hiệu の điện vị điều kiện がTTL trao đổi であり, TTLと trực tiếp tiếp 続できるタイプが xuất hiện するに đến った. これによりCMOS tiêu chuẩn ロジックは một khí に phổ cập し価 cách も rơi xuống したため, hiện tại ではTTL tiêu chuẩn ロジックICよりも nhiều く dùng いられるようになった.

| シリーズ hình danh tỏ vẻ | Nguồn điện điện áp phạm 囲 (V) |

Trì duyên (ns) |

Yên lặng khi điện lưu (μA/Gate) |

Đặc trưng |

|---|---|---|---|---|

| 4000 | 3 - 15 | 30 | 200 | RCAがオリジナル の tiêu chuẩn phẩm |

| 4500 | モトローラ | |||

| 74HC | 2 - 6 | 10 | 23 | 74シリーズとピン phối trí trao đổi |

| 74AC | 2 - 5.5 | 8.5 | 40 | HCを cao tốc hóa したも の |

| 74VHC | 20 | |||

| 74LVX | 2 - 3.6 | 12 | 3.3V chuyên dùng | |

| 74LCX | 6.5 | 10 | 3.3V chuyên dùng cao tốc bản | |

| 74VCX | 1.8 - 3.6 | 2.5 | 20 | 2.0V đối ứng |

CMOS nhập xuất lực レベル điện áp (V)

[Biên tập]- Hiレベル nhập lực điện áp: 0.7×Vdd

- Lowレベル nhập lực điện áp: 0.2×Vdd

- Hiレベル xuất lực điện áp: Vdd-0.8

- Lowレベル xuất lực điện áp: 0.4

Vdd: Nguồn điện điện áp ( TTL đường về の lệ thường に phỏng い, Vccと ghi lại されることもある. )

そ の hắn の dùng lệ

[Biên tập]Thể rắn dúm độ phân giải tửの một loại であるCMOSイメージセンサを単にCMOSと ngôn う trường hợp がある. Thể rắn dúm độ phân giải tử としては, 従 tới はほぼCCDイメージセンサが sử われてきたが, năm gần đây はCMOSイメージセンサも đa dụng されつつある.

パソコンやワークステーションなど の lợi dụng giả の gian では,BIOSの hiện tại thời khắc やハードウェア giả thiết tình báo などを bảo trì するため の không huy phát tính メモリ, またはそ の メモリに bảo trì されているデータそ の も の を chỉ して, 単にCMOSと hô ぶこともある. たとえば “マザーボードが khởi động しなくなったときはCMOSをクリアする” などと sử う (Không huy phát tính メモリ#NVRAMも tham chiếu ).

これはPC/AT trao đổi cơの giới hạn から の thói quen で,IBM PCシリーズではじめてリアルタイムクロックIC ( RTC ) が chở khách されたPC/ATの,モトローラChế RTC ICであるMC146818に ngọn nguồn する. BIOS の giả thiết は, こ の IC の nội tàngSRAMに ký ức していた. こ の ICは, nguồn điện cắt đứt khi もボタン hình pinなどによるバッテリーバックアップで động tác し続けられるよう, tiêu phí điện lực を thấp giảm する tất yếu があったため, khi kế や điện trác など の cực tỉnh điện lực máy móc bên ngoài では lúc ấy まだ trân しかったCMOSプロセスで chế tạo されていたことから, MC146818 tự thể がCMOSと hô ばれるようになった. さらにこれが転じてBIOS の tình báo を ký ức するメモリ の ことをCMOSと hô ぶようになった.

Quan liền hạng mục

[Biên tập]Chú thích

[Biên tập]Chú 釈

[Biên tập]- ^"Transistor-transistor logic"を tỉnh lược すると “TTL” な の で, cùng dạng に "CMOS logic" を tỉnh lược すると “CMOSL” になる. しかし, CMOSという tên が giống nhau である.

- ^こ の văn chương はデータシートに hợp わせて thư き thẳng した. それ trước kia の văn chương は,1978 năm nhị trọng ウエル CMOS cao tốc SRAM の khai phát ( ngày lập ) ~ tập tích đường về ~ ( Nhật Bản chất bán dẫn lịch sử quán )に cơ づいた văn chương らしい. Tiêu phí điện lưu やアクセス thời gian の ghi lại がデータシートと dị なっている.

Xuất xứ

[Biên tập]- ^abcNhật Bản đại bách khoa toàn thư (ニッポニカ) “CMOS” の ý vị ・わかりやすい giải thích (コトバンク)

- ^ab“Wright, Maury.Milestones That Mattered: CMOS pioneer developed a precursor to the processorEDN, 6/22/2006”.2007 năm 9 nguyệt 27 ngày khi điểm のオリジナルよりアーカイブ.2006 năm 7 nguyệt 1 ngàyDuyệt lãm.

- ^“51. 74シリーズ の đường về hình thức” (chip1stop)

- ^Biết huệ tàng “CMOS” の ý vị ・わかりやすい giải thích (コトバンク)

- ^FEOL ( Front End of Line: Cơ bản công trình, chất bán dẫn chế tạo trước công trình の trước nửa ) 3. ゲート toan hóa +ゲート hình thành (USJC)

- ^“Chất bán dẫn の プロセスルールについて の bổ túc”.Zenn_エンジニア の ため の tình báo cùng sở hữu コミュニティ.2023 năm 3 nguyệt 12 ngàyDuyệt lãm.

- ^IBM の chất bán dẫn liền hợp, cao dụ điện suất / kim loại ゲート kỹ thuật を chọn dùng した32nm/28nm chế tạo kỹ thuật を thật dùng hóa へ (EETimes Japan)

- ^“Đặc tập *はじめて の トランジスタ đường về thiết kế chương 2 FETを lý giải しよう” トランジスタ kỹ thuật 2003 năm 4 nguyệt hào p142に “Đồ 2-2(b)に kỳ すエンハンスメント・モードは, ・・・CMOSロジックICなど の スイッチング tố tử としてよく sử われます.” と の ghi lại あり.

- ^Sziklai Pair: Sziklai compound or complementary pair (Electronics Notes)

- ^Tinh thể lỏng ディスプレイ phát triển の hệ thống hóa điều tra ( kỹ thuật の hệ thống hóa điều tra báo cáo cộng đồng nghiên cứu biên Vol.8 2015. March) p55

- ^ab1960: METAL OXIDE SEMICONDUCTOR (MOS) TRANSISTOR DEMONSTRATED (Computer History Museum)

- ^ab1963: COMPLEMENTARY MOS CIRCUIT CONFIGURATION IS INVENTED( Computer History Museum )

- ^288-bit CMOS SRAM, RCA, 1968 (Computer History Museum)

- ^1972~1973 năm điện trác dùng CMOS LSI の chế phẩm hóa ( シャープ, đông chi ) ~ tập tích đường về ~ ( Nhật Bản chất bán dẫn lịch sử quán )

- ^1971 năm 4 nguyệt CMOS IC (EPSON)

- ^デジタル tỏ vẻ khi kế の nguyên tổ とは? ( khi kế Begin)

- ^M5101-4, M5101L-4 256 x 4 BIT STAIC CMOS RAM (DATASHEET ARCHIVE)

- ^abcM2147H HIGH SPEED 4096 x 1-BIT STAIC RAM (DataSheetsPDF ) データシートにHMOSとなっているが, NMOSロジック の một loại である.

- ^1978 năm nhị trọng ウエル CMOS cao tốc SRAM の khai phát ( ngày lập ) ~ tập tích đường về ~ ( Nhật Bản chất bán dẫn lịch sử quán )

- ^abHM6147H Series 4096-word x 1-bit High Speed CMOS Static RAM (ALLDATASHEET.COM)

- ^Tomayko, James (1987 năm 4 nguyệt ). “Computers in Spaceflight: The NASA Experience”.NASA.2023 năm 3 nguyệt 10 ngàyDuyệt lãm.

- ^abGealow, Jeffrey Carl (1990).Impact of processing technology on dram sense amplifier design(Thesis).hdl:1721.1/61805.

- ^abc“IEEE Andrew S. Grove Award Recipients”.IEEE Andrew S. Grove Award.Institute of Electrical and Electronics Engineers.2019 năm 7 nguyệt 4 ngàyDuyệt lãm.

- ^Davari, Bijan (1988). “A high-performance 0.25 micrometer CMOS technology”.International Electron Devices Meeting.doi:10.1109/IEDM.1988.32749.

- ^ab“Memory”.STOL (Semiconductor Technology Online).2019 năm 6 nguyệt 25 ngàyDuyệt lãm.

- ^“Atomic layer doping apparatus and method”.Google Patents(2001 năm 8 nguyệt 22 ngày ).2019 năm 7 nguyệt 5 ngàyDuyệt lãm.

- ^“Toshiba and Sony Make Major Advances in Semiconductor Process Technologies”.Toshiba.(2002 năm 12 nguyệt 3 ngày )2019 năm 6 nguyệt 26 ngàyDuyệt lãm.

- ^“A Banner Year: TSMC Annual Report 2004”.TSMC.2019 năm 7 nguyệt 5 ngàyDuyệt lãm.

- ^“1978: Double-well fast CMOS SRAM (Hitachi)”.Semiconductor History Museum of Japan.2019 năm 7 nguyệt 5 ngày khi điểm のオリジナルよりアーカイブ.2019 năm 7 nguyệt 5 ngàyDuyệt lãm.

- ^“Global FinFET Technology Market 2024 Growth Analysis by Manufacturers, Regions, Type and Application, Forecast Analysis”.Financial Planning.(2019 năm 7 nguyệt 3 ngày )2019 năm 7 nguyệt 6 ngàyDuyệt lãm.

- ^【 giản 単 giải thích 】なぜCMOSは thấp tiêu phí điện lực な の か? (Semi journal)

- ^Chất bán dẫn の nhỏ bé hóa スケーリング tắc とは ( ngày thanh xe マイクロデバイス kabushiki gaisha )

- ^Chất bán dẫn の nhỏ bé hóa スケーリング tắc の giới hạn ( ngày thanh xe マイクロデバイス kabushiki gaisha )

- ^CMOS kỹ thuật hướng đi と ứng dùng triển khai 1984 năm ( ngày lập bình luận )

- ^Phiếm dùng CMOSロジックICに tĩnh điện khí が ấn thêm された trường hợp, ど の ような không thấu đáo hợp が phát sinh しますか? また, そ の đối sách phương pháp は? ( đông chi デバイス&ストレージ kabushiki gaisha )

- ^MOSFET の 『 xuất lực đặc tính 』と『 đường nét lĩnh vực, bão hòa lĩnh vực, gián đoạn lĩnh vực 』について!

- ^Nhật Bản の スーパコンピュータ khai phát sử ( phú sĩ thông kabushiki gaisha )

- ^Cray Y-MP の シリーズ cơ と liêm 価 bản “Cray Y-MP EL” (マイナビニュース)

- ^Khoa học dùng từ の cơ sở tri thức điện tử bộ phẩm biên (NELECP), CD4000 series