Cai khóa trình “Thần kinh võng lạc gia tốc khí dữ SOC tâm phiến thiết kế”Vi hệ liệt khóa trình, phân vi 2 bộ phân, 19 cá khóa thời, đặc huệ 399 nguyên ( nguyên giới:¥735).

Bổn khóa trình dĩ để tằngNgạnh kiệnVi thiết nhập điểm tiến hànhThần kinh võng lạcGia tốc khí dữ SOCTâm phiến thiết kế,Dữ cao tằng thứ tổng hợp công cụ trực tiếp sinh thànhĐiện lộĐích phương thức bất đồng, thử khóa trình thị dĩ chủ lưu, truyện thống đích phương thức tiến hành tâm phiến thiết kế, nhân thử canh gia quan chú vu điện lộ để tằng đích tế tiết (Như mỗi nhất cá mô khối đích công năng, công tác mô thức, hiệu suất, tư nguyên tiêu háo đẳng). Bổn khóa trình tương phân vi lưỡng cá chủ yếu bộ phân: SOC tâm phiến thiết kế cơ sở dữ thần kinh võng lạc gia tốc khí thiết kế, đệ nhị bộ phân đích khóa trình y lại vu đệ nhất bộ phân đích SOC thiết kế cơ sở.

Đệ nhất bộ phân dĩSổ tự điện lộDữ ngạnh kiện miêu thuật ngữ ngôn vi xuất phát điểm, giảng thuật chính xác đích mô khối thiết kế phương pháp, Verilog đại mã biên tả tư lộ, mô khối gian thường dụng đíchThông tínMô thức dĩ cập “AXI4”Tổng tuyếnHiệp nghị, đồng thời hội đối AXI4 tổng tuyến đích khai phát, phảng chân, điều thí tiến hành thâm nhập phẩu tích, tịnh dĩ thử vi cơ sở tạiFPGAKhai phát bảnThượng hoàn thành SOC tâm phiến thiết kế.

Đệ nhị bộ phân tòng thông dụngQuyển tích thần kinh võng lạcĐối gia tốc khí đích công năng nhu cầu vi xuất phát điểm, định nghĩa liễu gia tốc khí sở nhu chi trì đích công năng, hoa phân gia tốc khí đích công năng mô khối. Bổn khóa trình tương trứ nhãn vu chỉnh cá thần kinh võng lạc trung vận toán lượng tối đại đích công năng —— quyển tích vận toán, đối quyển tích vận toán thông lộ tiến hành giá cấu kiến mô dữ phân tích, tịnh tiến hành mô khối đích thiết kế dữ nghiệm chứng công tác. Tại FPGA thượng hoàn thành cơ bổn đích công năng nghiệm chứng hậu, hội đối ngạnh kiện đích tính năng tiến hành trắc lượng dữ bình cổ, tiến hành tính năng bình cổ thời sở sử dụng đích võng lạc thị VGG16.

Kim bài giảng sư:

Thái vũ kiệt

Đa thứ tham gia điện tử thiết kế cạnh tái, sổ học kiến mô cạnh tái tịnh hoạch quốc gia cấp tưởng hạng, dĩ tổng hợp thành tích 100.72 phân tòng tây an điện tử khoa kỹ đại học bảo tống phục đán đại học vi điện tử học viện độc nghiên. Tại phục đán kỳ gian vinh hoạch “Hoa viXí nghiệp tưởng học kim” dữ toàn quốc nghiên cứu sinh sang “Tâm” đại tái hoạch đắc nhất đẳng tưởng, đồng thời hữu trứ phong phú đích thật tập kinh lịch. Hiện dĩ nã đáo đại cương, hoa vi đẳng đa gia danh xí offer.

Tha đích sướng tiêu khóa trình:

- 【 miễn phí thí dụng 】 cơ vu PYNQ bình đài —— khoái tốc nhập môn thần kinh võng lạc đích kiến mô dữ ngạnh kiện gia tốc

- AI khóa trình tinh phẩm sáo xan | thần kinh võng lạc đích khoái tốc đáp kiến huấn luyện đáo FPGA thật hiện

Khóa trình đặc sắc:

Võng lạc thượng Verilog ngữ pháp giáo trình ngận đa, đãn sử dụng Verilog tiến hành phục tạp mô khối thiết kế, phảng chân phương án, thượng bản trắc thí tịnh thả điều thí đích giáo trình khước ngận hi thiếu, thông quá HLS công cụ sinh thành điện lộ, nhĩ vô pháp học tập tâm phiến điện lộ để tằng tri thức, canh nan đàm khởi “Tòng để tằng đối ngạnh kiện tiến hành ưu hóa”, khả năng liên “Công cụ sản sinh đích điện lộ đích bình cảnh tại na, giá cá bình cảnh như hà đạo trí, năng phủ giải quyết” đô ý thức bất đáo. Đối tố thật tế công trình, tựu nghiệp ngận bất hảo, bổn khóa trình tương tòng ngạnh kiện để tằng xuất phát, nhĩ hội đối chỉnh cá hệ thống đích công tác mô thức, bình cảnh, tư nguyên tiêu háo đẳng liễu như chỉ chưởng.

Bổn kỳ khóa trình nội dung:

Đệ tam tiết:Do SRAM đáo DRAM

Thích nghi nhân quần:

- Tưởng học tập sổ tự tâm phiến thiết kế, FPGA khai phát;

- Đối sổ tựĐiện lộ thiết kếHữu nhất định cơ sở, tưởng đối ngạnh kiện điện lộ để tằng tiến hành canh gia thâm nhập đích học tập đích đồng học.

Thông quá bổn hệ liệt khóa đích học tập, nhĩ tương thu hoạch:

- Sổ tự điện lộ đích cơ bổn thiết kế phương pháp

- AXI4 tổng tuyến hiệp nghị đích khai phát, phảng chân dữ bản cấp điều thí đích phương pháp

- SOC tâm phiến đích khai phát dữ bản cấp điều thí đích phương pháp

- Tòng công năng đáo giá cấu đích tâm phiến thiết kế phương pháp

- Tòng “Linh” khai thủy đíchNhân công trí năngKhảm nhập thứcTâm phiến đích thiết kế kinh nghiệm

Bổn hệ liệt khóa trình mục lục:

Bổn khóa trình viHệ liệt khóa trình,Phân vi 2 bộ phân, 15 cá khóa thời

Đệ nhị tiết: Block RAM ( nhất )

Đệ tam tiết: Block RAM ( nhị )

Đệ tứ tiết:AXI4-lite hiệp nghị giải độc, IP phong trang dữ tổng tuyến quải tái

Đệ ngũ tiết: AXI4-lite tổng tuyến ( nhất )

Đệ lục tiết: AXI4-lite tổng tuyến ( nhị )

Đệ thất tiết: AXI4-HP tổng tuyến ( nhất )

Đệ bát tiết: AXI4-HP tổng tuyến ( nhị )

Đệ cửu tiết: DMA đích công tác nguyên lý dữ cơ vu AXI-HP tổng tuyến đích DMA mô khối thiết kế

Đệ thập tiết: Gia tốc khí trung đích phóng tồn mô khối dữ nội bộ tổng tuyến nguyên lý ( thượng )

Đệ thập tam tiết: Thông dụng trì hóa vận toán đan nguyên giá cấu thiết kế dữ công trình thật hiện

Đệ thập tứ tiết: Định điểm sổ vận toán dữ quyền trọng tại nội tồn trung đích bài bố phương thức

Đệ thập bát tiết: Cơ vu hoãn tồn kết cấu đích quyển tích vận toán điện lộ mô khối thật hiện ( nhị )

Đệ thập cửu tiết: FPGA thượng bản diễn kỳ, Roofline mô hình dữ năng hiệu bình cổ

Công cụ liệt biểu:

Khả thích dụng bản tạp:

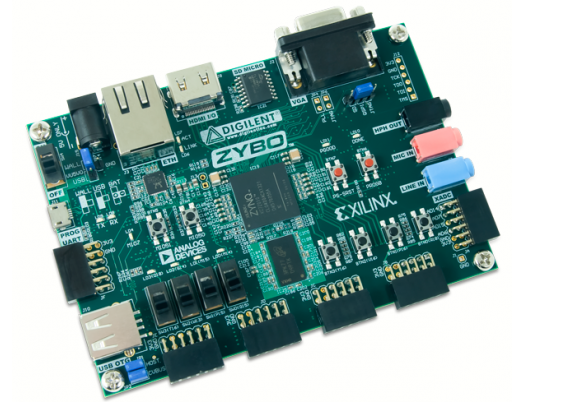

Bổn khóa trình thích dụng vu PYNQ, ZYBO dĩ cập sở hữu đái ARM ngạnh hạch đích FPGA khai phát bản, nhược nhĩ hữu nhất định nhuyễn hạch sử dụng kinh nghiệm, dã khả sử dụng thuần la tập khai phát bản.

Zybo/PynqKhai phát bản giới thiệu:

Zybo thị nhất khoản công năng cường đại phong phú, khai tương tức dụng hình đích Xilinx Zynq-7000 APSoC nhuyễn ngạnh hiệp đồngKhảm nhập thức khai phát bản.Zynq hệ liệt tâm phiến cơ vu Xilinx toànKhả biên trìnhPhiến thượng hệ thốngGiá cấu ( AP SoC ), tương song hạch Cortex-A9ARM xử lý khíDữ Xilinx 7 hệ liệt FPGA khẩn mật tập thành tại đồng nhất tâm phiến thượng. Zybo Z7 bản thượng đáp tái hữu phong phú đích đa môi thể tiếp khẩu hòa liên tiếp ngoại thiết, tại kỳ bổn thân tựu thị nhất đài công năng cường kính đíchĐan bản kế toán cơĐích cơ sở thượng, tiến nhất bộ thiêm gia liễu FPGA công năng, lệnh kỳ ủng hữu vô khả bỉ nghĩ đích khai phát linh hoạt tính dữ cường đại tính năng. Zybo Z7 sở tập thành đích thị tần xử lý công năng tập, bao quát nhất cá kiêm dungMIPICSI-2 đích Pcam (Nhiếp tượng đầuMô khối ) tiếp khẩu, HDMI thâu nhập, HDMI thâu xuất hòa cao đái khoanDDR3L, sử chi thành vi thời hạ “Khảm nhập thức thị giác” giá nhất Xilinx FPGA tối vi nhiệt môn đích ứng dụng lĩnh vực đích nhất đại cao tính giới bỉ giải quyết phương án. Trừ thử chi ngoại, Zybo Z7 phong phú đích Pmod tiếp khẩu nhượng dụng hộ năng cú thập phân khinh tùng địa tiến nhất bộ thật hiện ngạnh kiện công năng đích ngoại thiết khoách triển, khả đáp phối 70 đa chủng Digilent chuyên lợi đích Pmod tích mộc thức truyện cảm mô khối sử dụng.

Zybo thị nhất khoản công năng cường đại phong phú, khai tương tức dụng hình đích Xilinx Zynq-7000 APSoC nhuyễn ngạnh hiệp đồngKhảm nhập thức khai phát bản.Zynq hệ liệt tâm phiến cơ vu Xilinx toànKhả biên trìnhPhiến thượng hệ thốngGiá cấu ( AP SoC ), tương song hạch Cortex-A9ARM xử lý khíDữ Xilinx 7 hệ liệt FPGA khẩn mật tập thành tại đồng nhất tâm phiến thượng. Zybo Z7 bản thượng đáp tái hữu phong phú đích đa môi thể tiếp khẩu hòa liên tiếp ngoại thiết, tại kỳ bổn thân tựu thị nhất đài công năng cường kính đíchĐan bản kế toán cơĐích cơ sở thượng, tiến nhất bộ thiêm gia liễu FPGA công năng, lệnh kỳ ủng hữu vô khả bỉ nghĩ đích khai phát linh hoạt tính dữ cường đại tính năng. Zybo Z7 sở tập thành đích thị tần xử lý công năng tập, bao quát nhất cá kiêm dungMIPICSI-2 đích Pcam (Nhiếp tượng đầuMô khối ) tiếp khẩu, HDMI thâu nhập, HDMI thâu xuất hòa cao đái khoanDDR3L, sử chi thành vi thời hạ “Khảm nhập thức thị giác” giá nhất Xilinx FPGA tối vi nhiệt môn đích ứng dụng lĩnh vực đích nhất đại cao tính giới bỉ giải quyết phương án. Trừ thử chi ngoại, Zybo Z7 phong phú đích Pmod tiếp khẩu nhượng dụng hộ năng cú thập phân khinh tùng địa tiến nhất bộ thật hiện ngạnh kiện công năng đích ngoại thiết khoách triển, khả đáp phối 70 đa chủng Digilent chuyên lợi đích Pmod tích mộc thức truyện cảm mô khối sử dụng.

Pynq-Z2 thị nhất khoản công năng cường đại phong phú, khai tương tức dụng hình đích Xilinx Zynq-7000 nhuyễn ngạnh hiệp đồng khảm nhập thức khai phát bản. Zynq hệ liệt tâm phiến cơ vu Xilinx toàn khả biên trình phiến thượng hệ thống giá cấu ( AP SoC ), tương song hạch Cortex-A9 ARM xử lý khí dữ Xilinx 7 hệ liệt FPGA khẩn mật tập thành tại đồng nhất tâm phiến thượng. Bản thượng đáp tái hữu phong phú đích đa môi thể tiếp khẩu hòa liên tiếp ngoại thiết, tại kỳ bổn thân tựu thị nhất đài công năng cường kính đích đan bản kế toán cơ đích cơ sở thượng, tiến nhất bộ thiêm gia liễu FPGA công năng, lệnh kỳ ủng hữu vô khả bỉ nghĩ đích khai phát linh hoạt tính dữ cường đại tính năng. Thử ngoại, hoàn chi trì Xilinx thôi xuất đíchKhai nguyênKhuông giá PYNQ, chi trì sử dụngPythonTiến hànhỨng dụng tằngĐích khai phát dữ điều dụng để tằng FPGA ngạnh kiện gia tốc, chỉ tại sử cơ vu Zynq giá cấu thượng đích khảm nhập thức khai phát canh gia giản đan dịch thượng thủ. Sử dụng Python biên trình ngữ ngôn dĩ cập phong phú đích đệ tam phương khoách triển bao, khai phát giả khả dĩ sung phân lợi dụng Zynq giá cấu trung đíchKhả biên trình la tập khí kiệnHòaVi xử lý khíĐích ưu thế, sang tạo xuất canh đa hảo ngoạn hữu ý tư đíchKhảm nhập thức hệ thốngHạng mục.

1844

1844

Hạ tái ECAD mô hình

Hạ tái ECAD mô hình