Hardware thiết kế

Đối vuIntelBình đài, tựICLLake khai thủy, tựu bất tái chi trìLPC,Cận chi trì eSPI.

Dĩ TGL bình đài vi lệ,Ngạnh kiệnThiết kế thượng nhu yếu chú ý như hạ lưỡng điểm.

Nhất, Hardware StrapPin

GPP_C5, GPP_H0, GPP_H1, GPP_H2, tứ cá pin án thuận tự tổ thành 4-Bit Boot Strap Pin. Phối trí quy tắc như hạ biểu cách:

| 0000 = Master Attached Flash Configuration (BIOS/ CSME onSPI). eSPI is enabled |

|---|

| 0010 = Master Attached Flash Configuration (BIOS / CSME onSPI). eSPI is disabled |

| 0100 = BIOS on eSPI Peripheral Channel; CSME on masterattached SPI |

| 1000 = Slave Attached Flash Configuration (BIOS / CSME oneSPI attached device). |

| 1100 = BIOS on eSPI peripheral Channel; CSME on slaveattached SPI. |

Thường quy thiết kế đô thị MAF, eSPI Enable. Chính thường đích phối trí nhu yếu 0000, tứ cá pin nội bộ đô hữu 20K đích hạ lạp, nhân thử Strap Pin bảo trì Floating tức khả.

Chú ý: Bất đồngCPUBình đài, Strap Pin hữu soa dị, dĩ đối ứng bình đài EDS văn đương miêu thuật vi chuẩn.

Nhị, Flash Access

Vi liễu hàng đê ngạnh kiện thiết kế BOM thành bổn, CPU thiết kế thượng đề xuất MAF hòa SAF lưỡng chủng Flash cộng hưởng phương thức, dĩ tiết tỉnh EC Flash.

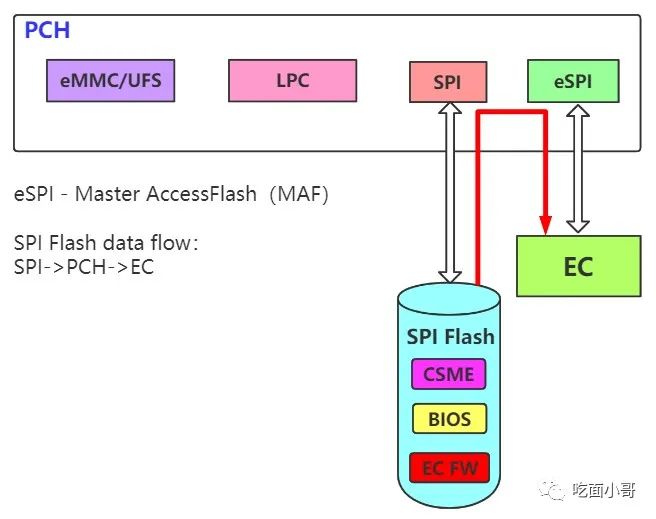

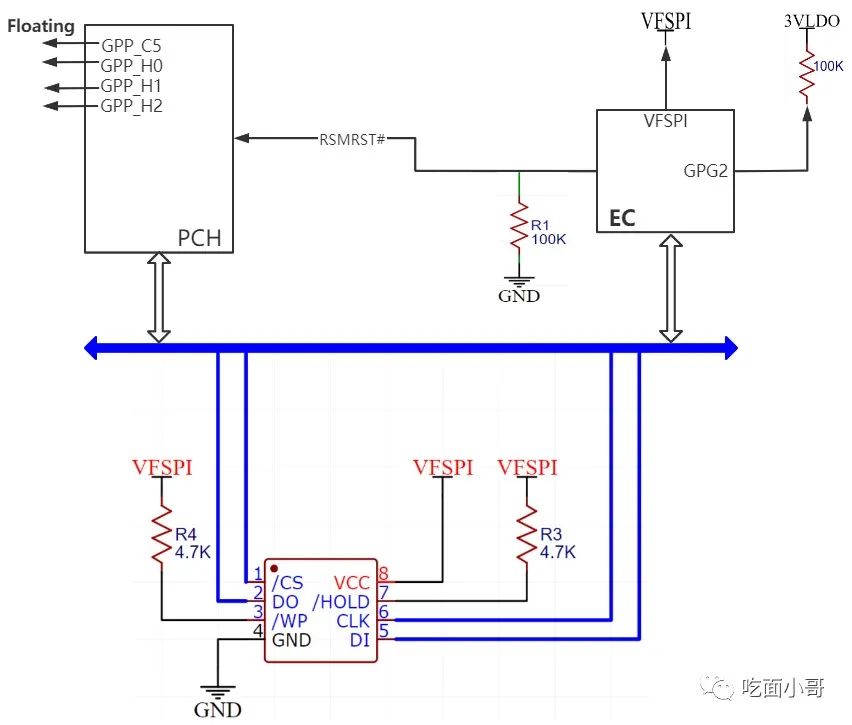

Master Attached Flash Sharing, như hạ đồ. EC thông quá eSPI phóng vấn PCH hạ SPI tổng tuyến thượng đích Flash, dĩ hoạch thủ EC Firmware.

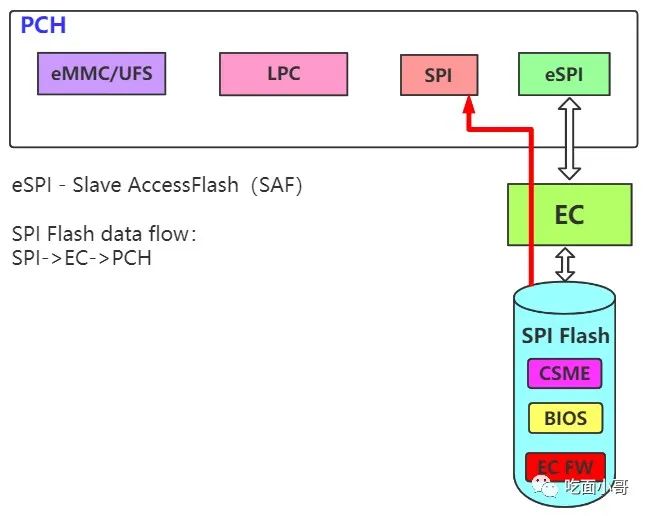

Slave Attached Flash Sharing, như hạ đồ. PCH thông quá eSPI thấu quá EC phóng vấn

BIOS, CSME Firmware.

Đối vu MAF thiết kế, nhu yếu bảo trì CPU bộ phân điện đả khai, xác bảo PCH nội eSPI hòa SPI khả dĩ công tác. EC tài hữu liễu thấu quá PCH eSPI Master phóng vấn Flash đích cơ sở.

Đối vu SAF thiết kế, BIOS, CSME Firmware thể lượng đại, PCH thấu quá EC phóng vấn, đối EC SPI Controller yếu cầu bỉ giác cao.

Sự thật thượng, PCH thông quá tự kỷ đích SPI Controller hoạch thủ BIOS, CSME, tựu xưng chi vi MAF. PCH thông quá eSPI hoạch thủ BIOS, CSME, tựu xưng chi vi SAF.

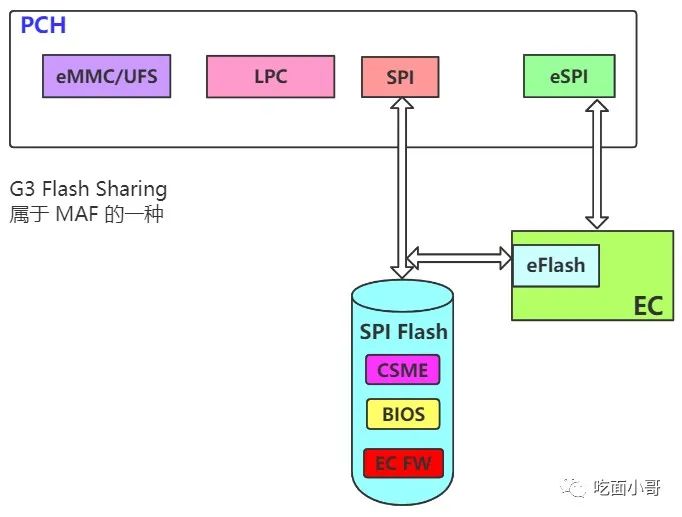

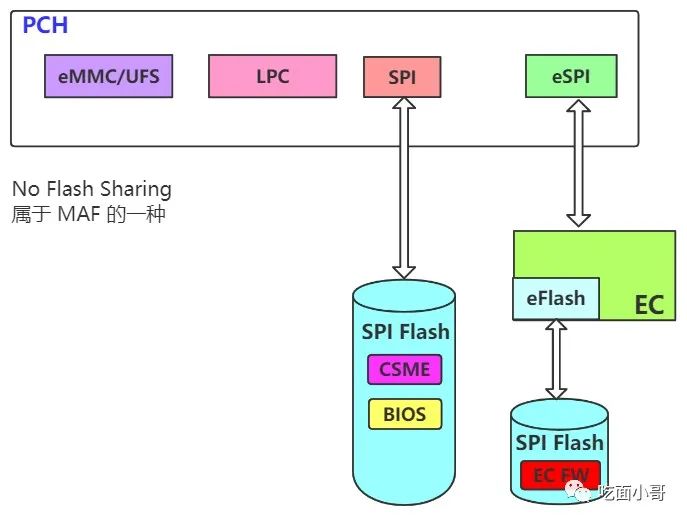

Thật tế ứng dụng trung, MAF hòa SAF giá lưỡng chủng Flash Sharing phương thức đô một hữu thải dụng. Nhi thị tuyển trạch

G3 Flash Sharing hoặc giả No Flash Sharing.

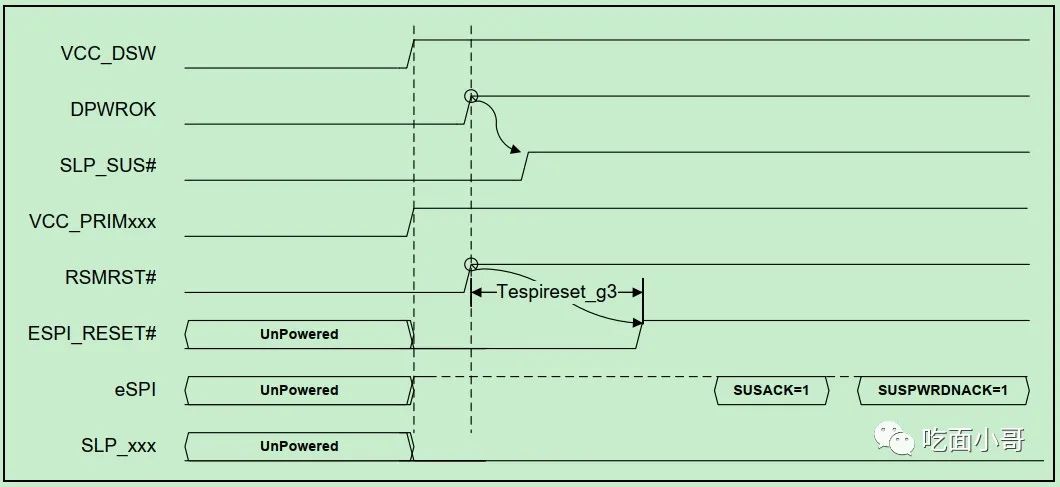

G3 Flash Sharing, như hạ đồ. PCH đích SPI hòa EC đích SPI tiếp tại nhất khởi, PCH thượng điện tiền hoặc giảRSMRST# lạp cao tiền, EC trực tiếp tòng SPITiếp khẩuĐộc thủ EC Firmware.

No Flash Sharing, như hạ đồ. PCH đích SPI hòa EC đích SPI phân biệt quải nhất cá Flash, hỗ bất càn thiệp.

Cơ vu thượng thuật G3 Flash Sharing thiết kế, thông thường ngạnh kiện thiết kế như hạ.

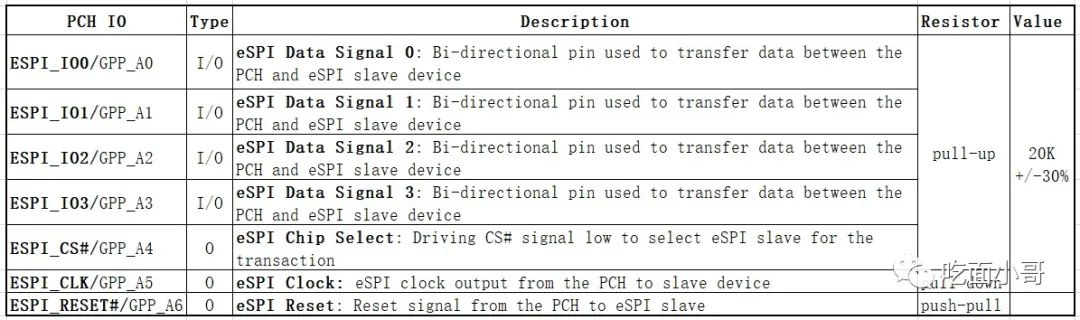

Tam, eSPI Pin List

PCH hòa EC đoan đích eSPI trực tiếp liên tuyến tức khả, thượng hạ lạp tại chip nội bộ hoàn thành.

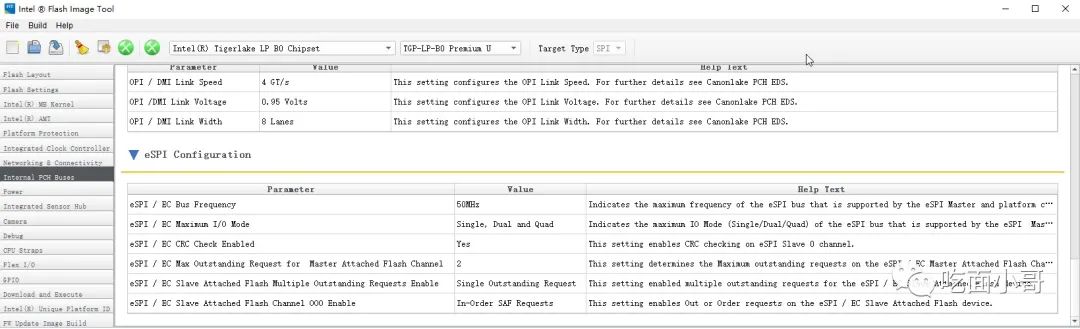

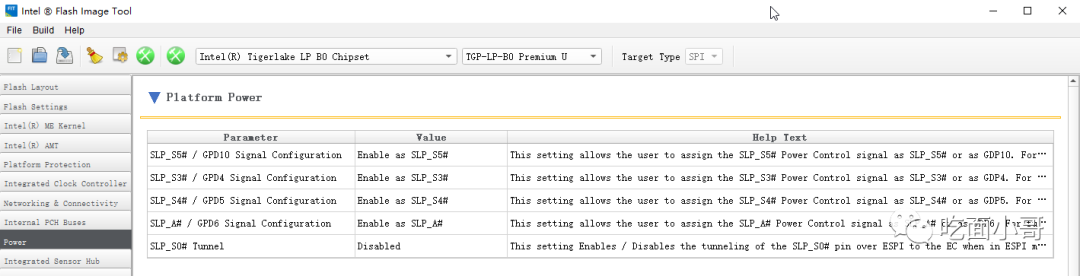

BIOS/ME phối trí

Sử dụng FIT phối trí METham sổ,Tức thiết trí PCH tác vi eSPI Master đích công tác tham sổ, dã xưng chi vi Soft-Strap. eSPI thông tấn tham sổ tối chung dĩ hòa EC câu thông kết quả vi chuẩn.

Quan vu FIT canh tường tế đích phối trí, nhu yếu căn cư hạng mục thật tế tình huống thiết định.

Boot lưu trình

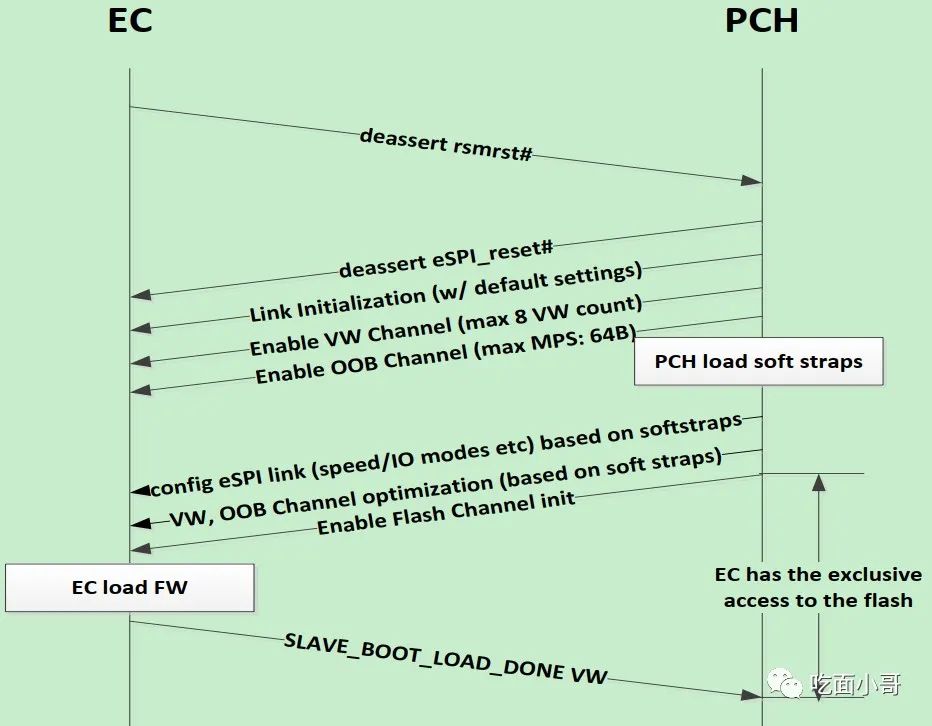

eSPI đích Boot lưu trình bao quát Channel Config, Flash Access, Virtual Wire Communication. MAFS hòa SAFS khải động quá trình lược hữu soa dị, thử xử dĩ MAFS khải động vi lệ.

eSPI thông đạo phối trí

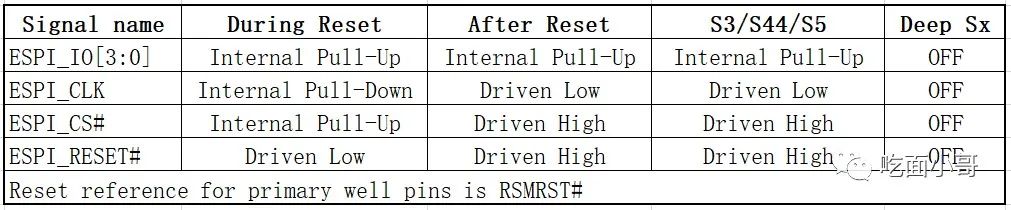

Đệ nhất bộ, EC lạp cao RSMRST# ( chi tiền đích thời tự án yếu cầu thao tác, đồng thời EC đoan đích eSPI Slave nhu yếu phục vị hoàn tất, chuẩn bị đãi mệnh ). Nhiên hậu PCH lạp cao eSPI_Reset#.

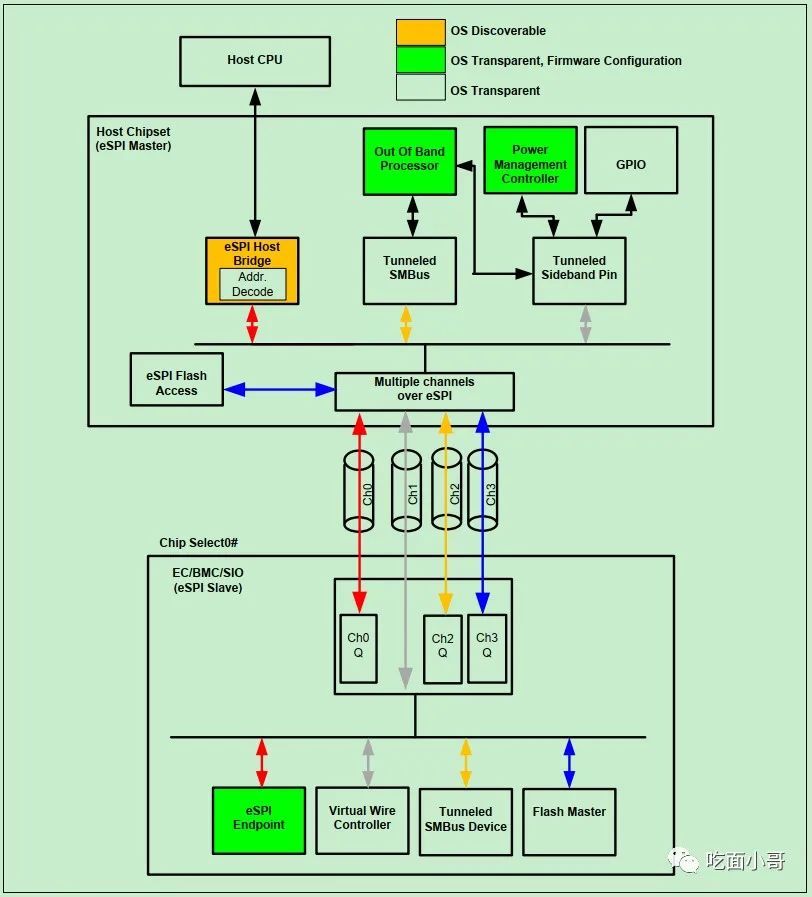

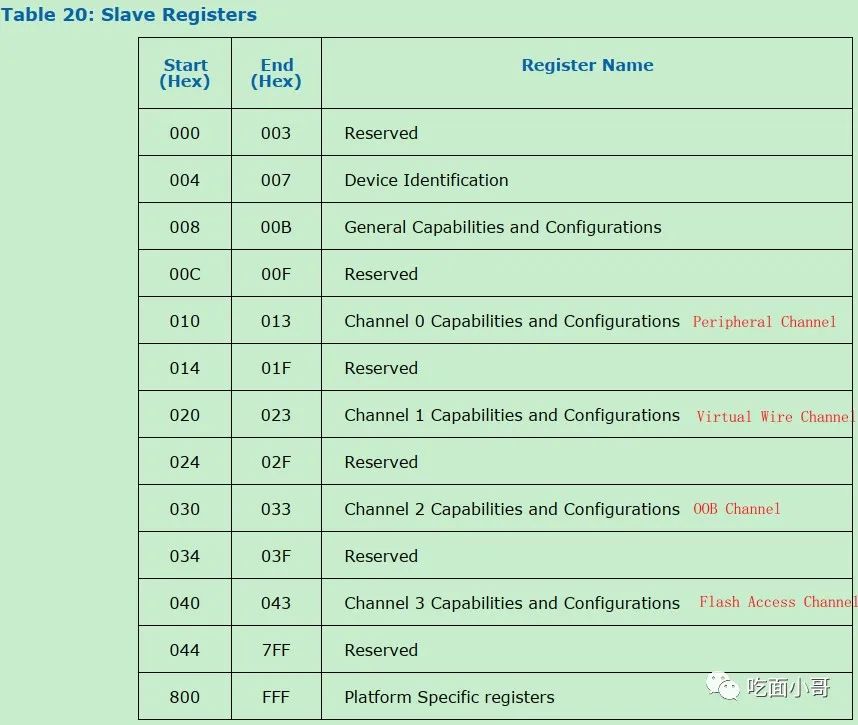

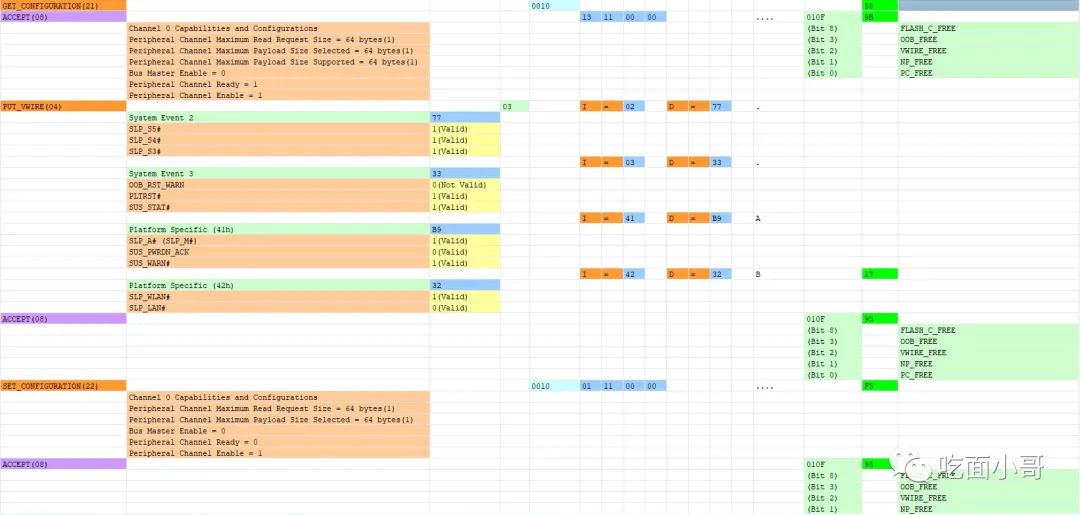

Đệ nhị bộ, eSPI-Master phối trí Peripheral, Virtual Wire, OOB, Flash Access tứ cá Channel. eSPI Master đoan đối Channel đích phối trí, tựu thị độc thủ Slave Channel phối tríKý tồn khí.Nhiên hậu căn cư Soft-Strap ( ME phối trí ) cải tả Slave đoan phối trí ký tồn khí, dĩ phối trí thật tế nhu cầu đích thông đạo thông tấn tham sổ. Như hạ đồ, Ch-0/1/2/3 phân biệt thị Peripheral, Virtual Wire, OOB, Flash Access Channel.

PCH tác vi eSPI Master phối trí Channel, cơ bổn la tập tựu thị eSPI Master độc thủ eSPI Slave ký tồn khí, cải tả ký tồn khí, hồi độc xác nhận. Ký tồn khí thao tác tối tiểu đan vị thị 4Byte. Sử dụng đáo đích chỉ lệnh thị GET_CONFIGURATION hòa SET_CONFIGURATION.

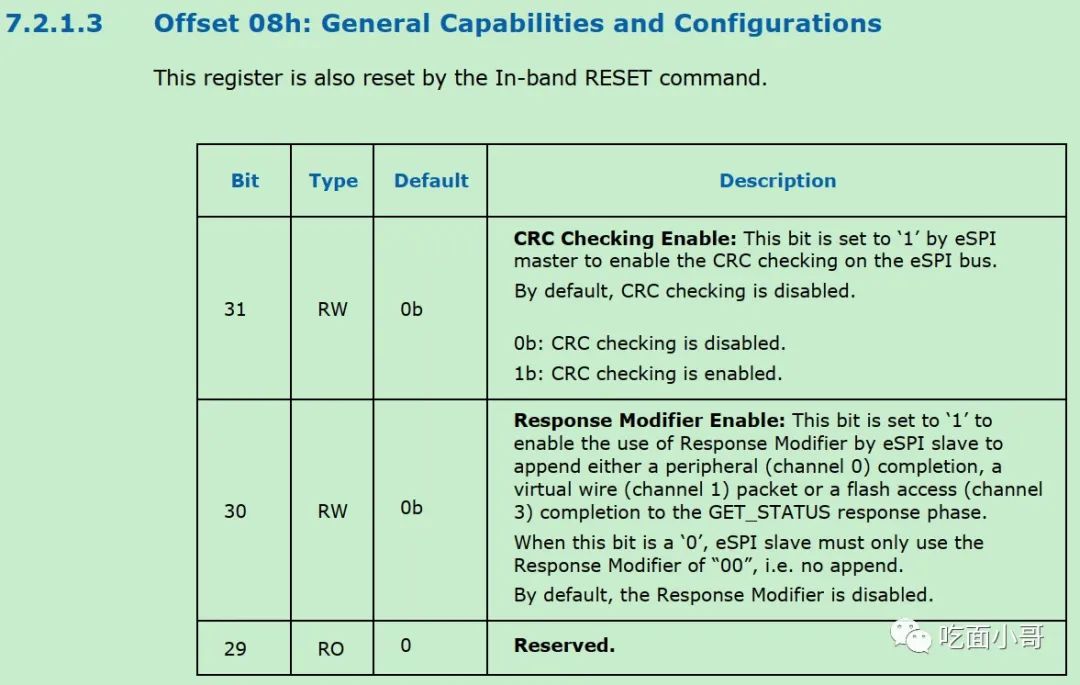

eSPI Slave đoan nhu yếu phối trí đích ký tồn khí chỉ hữu như hạ 5 cá, tức Offset 08, 10, 20, 30, 40, phân biệt đối ứng 4 cá Channel.

Ký tồn khí phối trí tế tiết khả dĩ tham khảo 《Enhanced Serial PeripheralInterface (eSPI) V1.0》

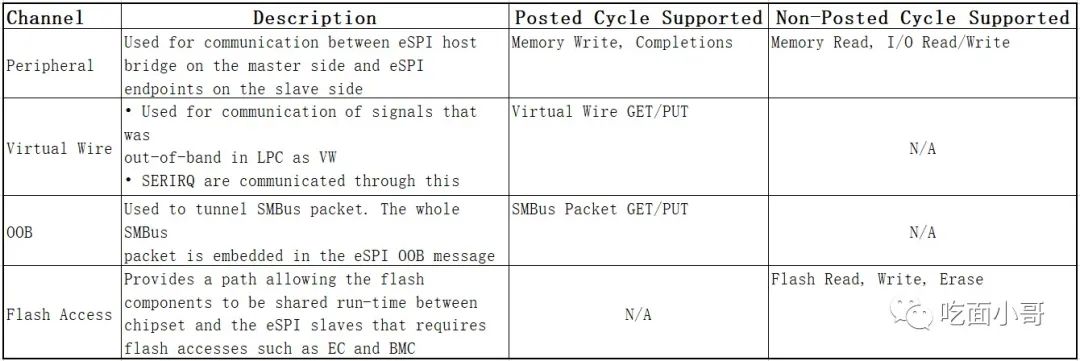

Mỗi cá Channel đích công năng như hạ biểu

Đệ tam bộ, Slave Boot Done

Phối trí hoàn Flash Access Channel, đối vu MAFS kết cấu lai thuyết, EC tựu khả dĩ thông quá eSPI phóng vấn PCH hạ đích SPI Flash liễu. EC ứng đương căn cư thật tế nhu yếu thông quá eSPI phóng vấn PCH SPI Controller hạ liên tiếp đích Flash, độc thủ EC Firmware.

Thật tế thượng, mục tiền thông dụng đích thiết kế thị Flash Sharing đích tiếp tuyến phương thức, EC tuy nhiên bất thông quá eSPI độc thủ Firmware. Đãn thị y cựu nhu yếu cấp Host phát tống nhất cá Virtual Wire Signal, tức SLAVE_BOOT_LOAD_DONE.

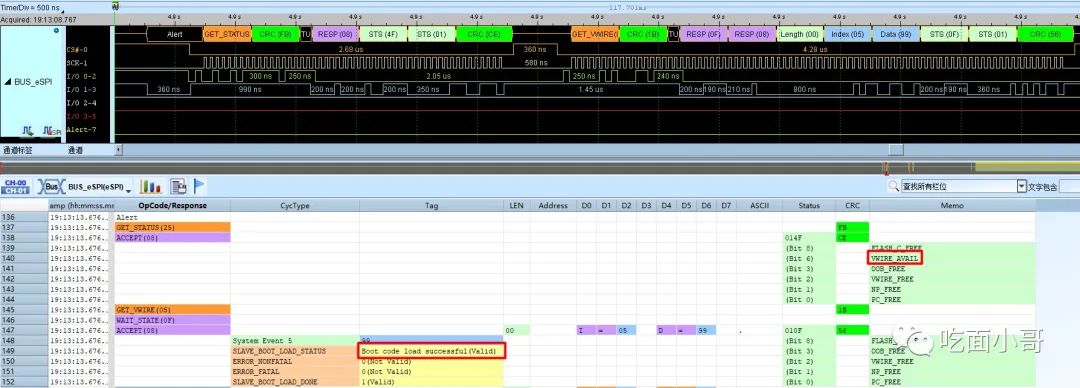

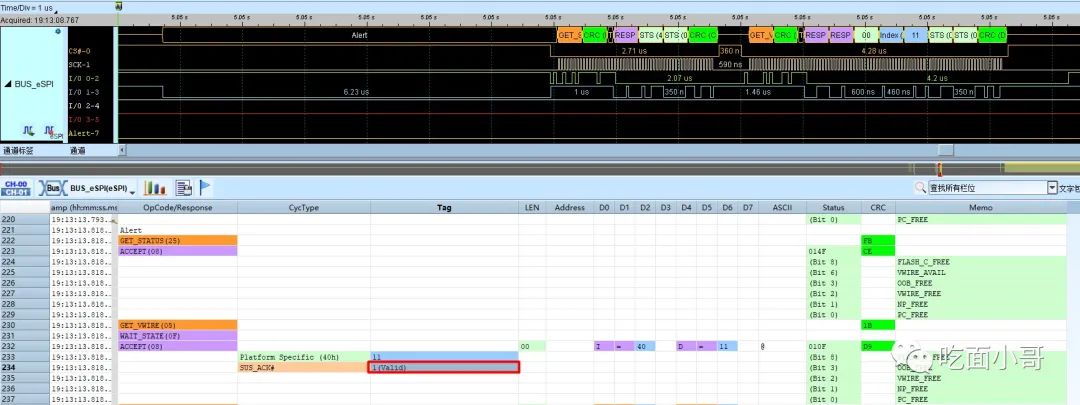

Slave đoan phát tống SLAVE_BOOT_LOAD_DONETín hàoCấp Host. Do vu thị Slave chủ động cấp Host phát tống, nhân thử tại CS# cao điện bình kỳ gian, Slave lạp đê I/O 1 sản sinh nhất cá ALERT# trực đáo Host đoan lạp đê CS# vi chỉ. Hạ đồ ALERT# lạp đê thời gian tựu vi 360ns.

Host khẩn tiếp trứ phát tống GET_STATUS mệnh lệnh, tra khán Slave đích Event, Slave trí vị BIT-6, biểu minh phát sinh liễu Virtual Wire sự kiện.

Host phát tống GET_VWIRE hoạch thủ thật tế đích Virtual Wire trạng thái.

Host độc thủ Virtual Wire trạng thái. Phát hiện SLAVE_BOOT_LOAD_DONE trí vị, Host tức khả tiến hành hạ nhất bộ Boot.

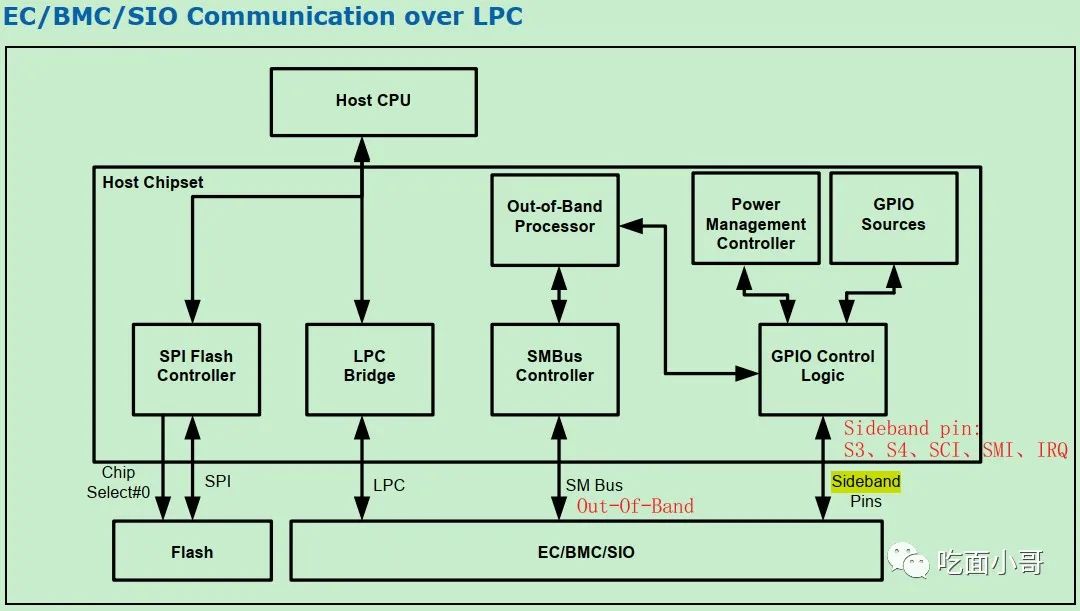

Virtual Wire giao hỗ

eSPI thiết kế đích nhất cá ưu thế tựu tại vu giảm thiếu dẫn cước tư nguyên, bả Sideband pin chuyển hoán vi in-band Message. Nhân thử PCH thâu nhập hoặc giả thâu xuất đích nhất ta pin dĩ kinh chuyển vi in-band Message.

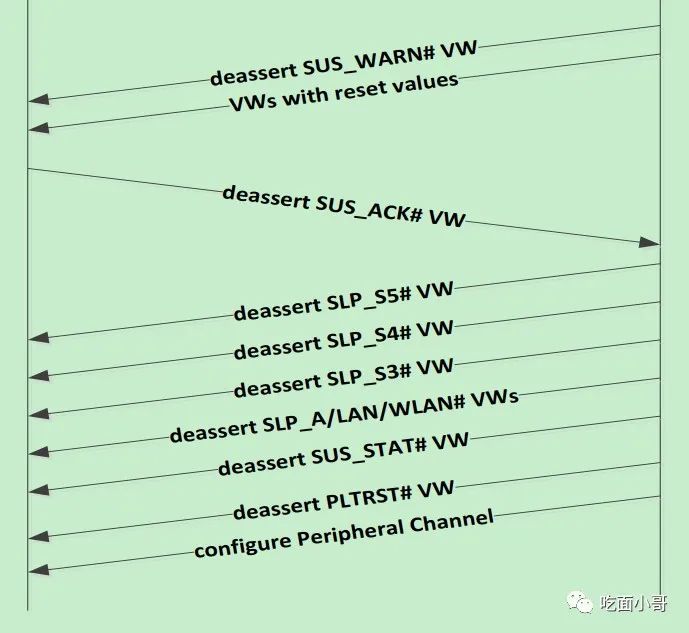

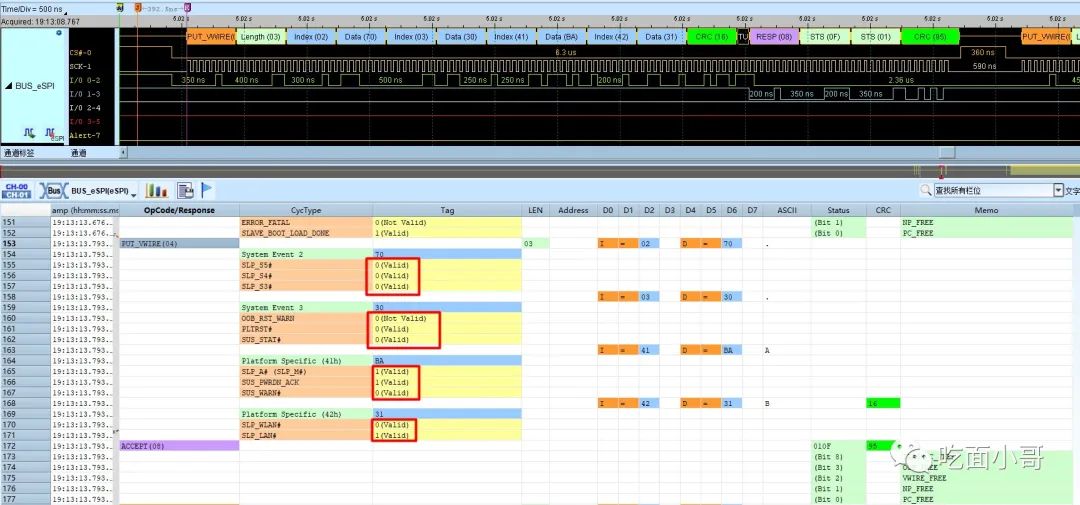

Đệ tứ bộ, eSPI Master ( PCH ) thông quá PUT_VWIRE chỉ lệnh bả sở hữu VW tín hào thiết trí vi phục vị trị.

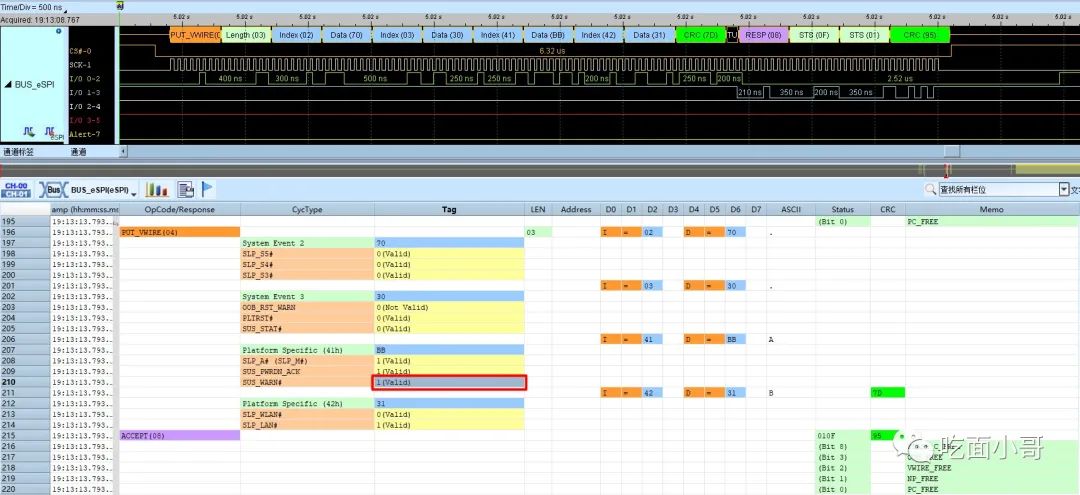

Đệ ngũ bộ, eSPI Master ( PCH ) phát tống SUS_WARN# = 1 đáo eSPI Slave. EC hồi phục SUS_AC# =1 đáo PCH

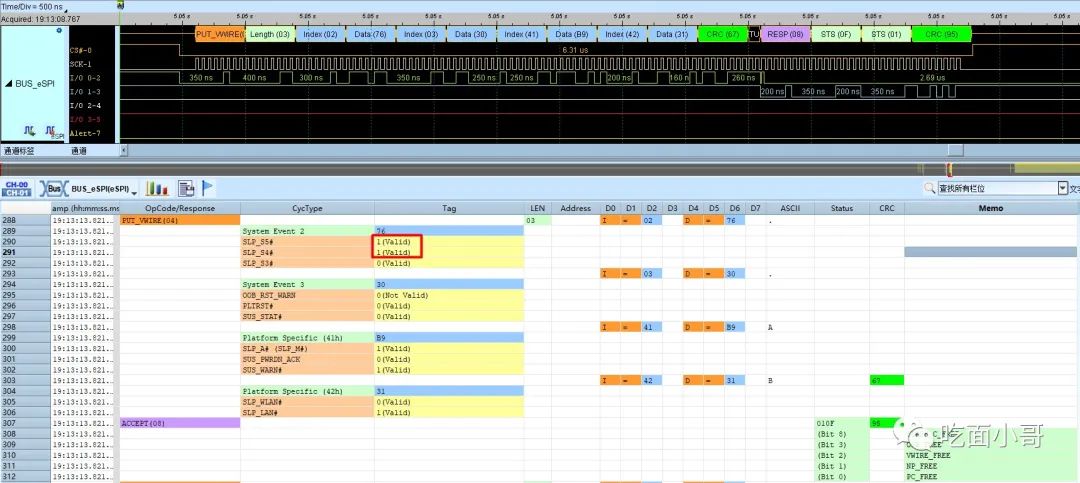

Đệ lục bộ, eSPI Master ( PCH ) ai cá nhi phát tống SLP_S5 / 4 / 3, SLP_A / LAN / WLAN cao tín hào đáo EC. Hạ đồ cận triển kỳ liễu SLP_S4/5.

Đệ thất bộ, eSPI Master ( PCH ) phát tống SUS_STAT# hòa RPLTRST# tín hào đáo EC. Giá tương hội sử năng Peripheral Channel.

Khẩn tiếp trứ eSPI Master căn cư Soft-Strap ( ME ) phối trí Peripheral Channel.

Chí thử, eSPI khải động tựu dĩ kinh hoàn thành, tiếp hạ lai tựu thị Memory, IO, OOB thông tấn.

Dĩ thượng lưu trình vi cá nhân lý giải, cận cung tham khảo.

-

cpu

+ quan chú

Quan chú

68Văn chương

10755Lưu lãm lượng

210205 -

intel

+ quan chú

Quan chú

19Văn chương

3476Lưu lãm lượng

185496 -

SPI

+ quan chú

Quan chú

17Văn chương

1679Lưu lãm lượng

90991 -

Tổng tuyến

+ quan chú

Quan chú

10Văn chương

2841Lưu lãm lượng

87814 -

Ngạnh kiện thiết kế

+ quan chú

Quan chú

18Văn chương

373Lưu lãm lượng

44497

Phát bố bình luận thỉnh tiênĐăng lục

Tương quan thôi tiến

eSPIHiệp nghị trảo bao phân tích

Thường kiếneSPIThông tấn sổ cư bao đích phân tích

PCB công nghệLưu trìnhTường giải

ESPI3 hồi thuESPI3 EMI trắc thí tiếp thu cơ

SPI dữeSPIPhân biệt thị thập ma ý tư

SOC đích đa hạchKhải độngLưu trìnhTường giải

PCB công nghệLưu trìnhTường giải

PCB gia côngLưu trìnhTường giảiĐại toàn

tft_espiHòa nodemcu liên tiếp

Chủ lưu đích thông tấn tổng tuyến LPC hòaeSPIGiới thiệu

eSPIThông tấn tổng tuyến đích ứng dụng ưu thế

AURIX™ TC3xxKhải độngLưu trìnhTường giải

PCB công nghệLưu trìnhTường giải.zip

PCB công nghệLưu trìnhTường giải.zip

eSPITiếp khẩu thông đạo công năng giải tích

eSPI khải động lưu trình tường giải

eSPI khải động lưu trình tường giải

Bình luận