- Hạ tái hải lượng tư liêu

- Học tập tại tuyến khóa trình

- Quan khán kỹ thuật thị tần

- Tả văn chương / phát thiếp / gia nhập xã khu

- Sang tác hoạt động

Hoàn thiện tư liêu nhượng canh đa tiểu hỏa bạn nhận thức nhĩ, hoàn năng lĩnh thủ20Tích phân nga,Lập tức hoàn thiện >

Tiêu thiêm>Verilog

Verilog HDL thị nhất chủng ngạnh kiện miêu thuật ngữ ngôn ( HDL:Hardware Description Language ), dĩ văn bổn hình thức lai miêu thuật sổ tự hệ thống ngạnh kiện đích kết cấu hòa hành vi đích ngữ ngôn, dụng tha khả dĩ biểu kỳ la tập điện lộ đồ, la tập biểu đạt thức, hoàn khả dĩ biểu kỳ sổ tự la tập hệ thống sở hoàn thành đích la tập công năng.

Văn chương:677Cá Thị tần:652Cá Lưu lãm:109537Thứ Thiếp tử:916Cá

( 1 ) fwrite thị nhu yếu xúc phát điều kiện đích, nhu yếu thủ động thiêm gia hoán hành. ( 2 ) như quả tả phóng văn kiện đích cách thức vi %d, tắc nhận vi thị vô phù hào sổ,

Verilog đáo VHDL chuyển hoán đích kinh nghiệm dữ kỹ xảo tổng kết

Verilog dữ VHDL ngữ pháp thị hỗ thông thả tương hỗ đối ứng đích, như hà tra khán nhị giả đối đồng nhất ngạnh kiện kết cấu đích miêu thuật, khả dĩ tá trợ EDA công cụ, như Vivado, đả khai Vivado hậu tha lí diện đích ngữ ngôn mô bản...

Cơ vu Verilog HDL đích FPGA đồ tượng lự ba xử lý phảng chân thật hiện

Chú ý giá lí đích A thị double loại hình đích, trực tiếp tiến hành imshow hội toàn bạch, yếu chuyển hóa đáo 0-1: A=A./255, hoặc giả bả double loại hình chuyển hóa vi chỉnh hình.

2024-04-26 Tiêu thiêm:FPGAVerilogĐồ tượng lự ba 292 0

Tại Verilog trung thật hiện Moore hình hòa Mealy hình trạng thái cơ đích phương pháp giản tích

Biên tả năng cú bị tổng hợp công cụ thức biệt đích trạng thái cơ, thủ tiên nhu yếu lý giải trạng thái cơ đích cơ bổn khái niệm hòa phân loại. Trạng thái cơ (FSM) thị biểu kỳ hữu hạn cá trạng thái dĩ cập tại giá ta trạng thái chi gian chuyển hoán đích la tập kết cấu.

2024-05-01 Tiêu thiêm:EDA công cụVerilogTrạng thái cơ 725 0

Tự truyện thâu bất biến đích 3 chủng đại tiểu đoan xử lý phương thức

Đại đoan, tối cao tự tiết tồn trữ tại tối đê đích nội tồn địa chỉ, tiểu đoan tắc thị tối đê hữu hiệu tự tiết tồn trữ tại tối đê đích nội tồn địa chỉ. Tại Verilog trung thật hiện đại đoan ( Big-Endian ) hòa tiểu đoan ( Little-E...

FPGA khai nguyên hạng mục: Verilog thường dụng khả tổng hợp IP mô khối khố

Sở hữu đại mã tại điển hình đích FPGA hòa chủ lưu FPGA cung ứng thương trung đô cụ hữu cao độ khả trọng dụng tính. Khả dĩ xuất vu nhậm hà mục đích đối văn kiện tiến hành trọng tân hỗn hợp, chuyển hoán hòa cấu kiến, thậm chí thị thương nghiệp dụng đồ.

2024-03-29 Tiêu thiêm:FPGAVerilogTổng tuyến 450 0

Học tập FPGA nhu yếu chưởng ác nhất hệ liệt đích tri thức hòa kỹ năng, chủ yếu bao quát dĩ hạ kỉ cá phương diện.

2024-03-27 Tiêu thiêm:FPGAVerilogSổ tự điện lộ 494 0

fpga khai phát nhu yếu chưởng ác na ta biên trình ngữ ngôn

FPGA ( hiện tràng khả biên trình môn trận liệt ) khai phát thiệp cập đa chủng biên trình ngữ ngôn hòa kỹ thuật.

2024-03-27 Tiêu thiêm:FPGAVerilogBiên trình ngữ ngôn 836 0

IC thiết kế trung trị đắc giải quyết đích tiểu vấn đề —screen như hà kiêm dung 256Color

Tùy trứ kế toán cơ ngạnh kiện đích cự đại tiến bộ, đồ hình giới diện đích trình tự trục tiệm chiêm cư liễu ứng dụng đích chủ lưu, bất quá Terminal đắc ích vu tính năng, đái khoan, dĩ cập truyện thống, kế thừa đẳng các chủng nhân tố, ứng dụng dã hoàn thị phi thường quảng phiếm đích.

2024-03-21 Tiêu thiêm:IC thiết kếVerilogVIM 1364 0

Cơ vu FPGA đích tịnh hành ADC dữ DAC Verilog thật hiện án lệ

Chuyển hoán đích y cư thị nhất cá giản đan đích vận toán quan hệ: “Bổ mã đích chỉnh sổ trị” + “Nguyên mã tuyệt đối trị đích chỉnh sổ trị” =2^B, B vi vị khoan. Bỉ như đái phù hào sổ nguyên mã 1110 đích bổ mã vi 1010: 1110 thủ tuyệt đối trị 0...

1

0

Cầu trợ các vị quan vu Verilog đương trung mô khối lệ hóa, đoan khẩu dữ dẫn cước đích vấn đề

Tiêu thiêm:FPGAVerilogverilog đại mã 643 1

2

0

Verilog đích bản bổn hữu na taLập tức hạ tái

Loại biệt:IC trung văn tư liêu 2024-05-31 Tiêu thiêm:Verilog 93 0

Verilog HDL sổ tự tập thành điện lộ thiết kế phương pháp khái thuậtLập tức hạ tái

Loại biệt:IC trung văn tư liêu 2024-02-03 Tiêu thiêm:Tập thành điện lộVerilog 150 0

verilog đích 135 cá kinh điển thật lệLập tức hạ tái

Loại biệt:C ngữ ngôn | nguyên đại mã 2024-02-02 Tiêu thiêm:Verilog 237 0

Cơ vu verilog đích vạn niên lịchLập tức hạ tái

Loại biệt:Điện tử tư liêu 2023-11-06 Tiêu thiêm:VerilogKế sổ 218 0

Cơ vu FPGA đích quang tiêm thông tín hệ thống đích thiết kế dữ thật hiệnLập tức hạ tái

Loại biệt:Điện tử tư liêu 2023-10-24 Tiêu thiêm:fpgaQuang tiêmThông tín hệ thống 200 0

Hắc kim Spartan6 khai phát bản đích Verilog giáo trình tường tế thuyết minhLập tức hạ tái

Loại biệt:FPGA/ASIC 2023-10-11 Tiêu thiêm:fpgaVerilogKhai phát bản 296 0

Khinh tùng thành vi thiết kế cao thủ Verilog_HDL thật dụng tinh giảiLập tức hạ tái

Loại biệt:Điện tử tư liêu 2023-09-13 Tiêu thiêm:Verilog 132 0

Verilog lệ trình Verilog HDL trình tự thiết kế giáo trìnhLập tức hạ tái

Loại biệt:Điện tử tư liêu 2023-08-16 Tiêu thiêm:VerilogHDLTrình tự 151 0

Verilog trung Pmod ALS đích SPI tiếp khẩu đại mãLập tức hạ tái

Loại biệt:Điện tử tư liêu 2023-06-15 Tiêu thiêm:VerilogSPIals 263 0

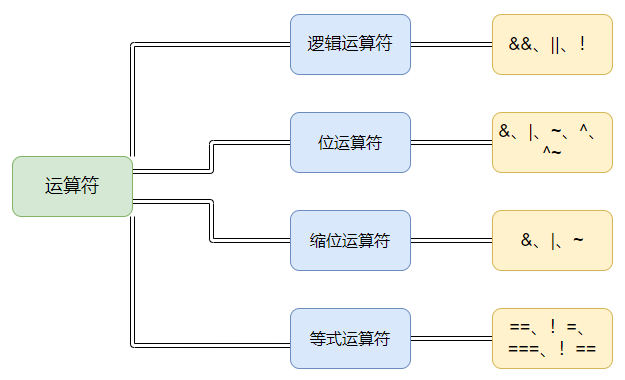

verilog đích la tập vận toán phù

Tả tại tiền diện chi tiền tằng kinh chỉnh lý quá verilog đích các loại vận toán phù đích biểu đạt phương thức, đãn thị tại học tập đích quá trình trung tịnh vị thâm nhập nghiên cứu quan vu la tập vận toán phù đích tương quan tri thức, đạo trí tại thật tế sử dụng quá trình trung thác ngộ tần xuất, hạ diện...

2023-09-21 Tiêu thiêm:VerilogSổ tự điện lộVận toán phù 1378 0

Nhất bổn Verilog HDL đại mã đối ứng điện lộ đích thư, trợ nhĩ khoái tốc biên tả khả tổng hợp mô hình

J.Bhasker thị IEEE PAR 1364.1 Verilog Synthesis Interoperability Working Group(...

Verilog trung đích If ngữ cú hòa case ngữ cú giới thiệu

Ngã môn tại thượng nhất thiên văn chương trung dĩ kinh khán đáo liễu như hà sử dụng trình tự khối ( lệ như always khối lai biên tả án thuận tự chấp hành đích verilog đại mã. Ngã môn hoàn khả dĩ tại trình tự khối trung sử dụng hứa đa ngữ cú lai khống...

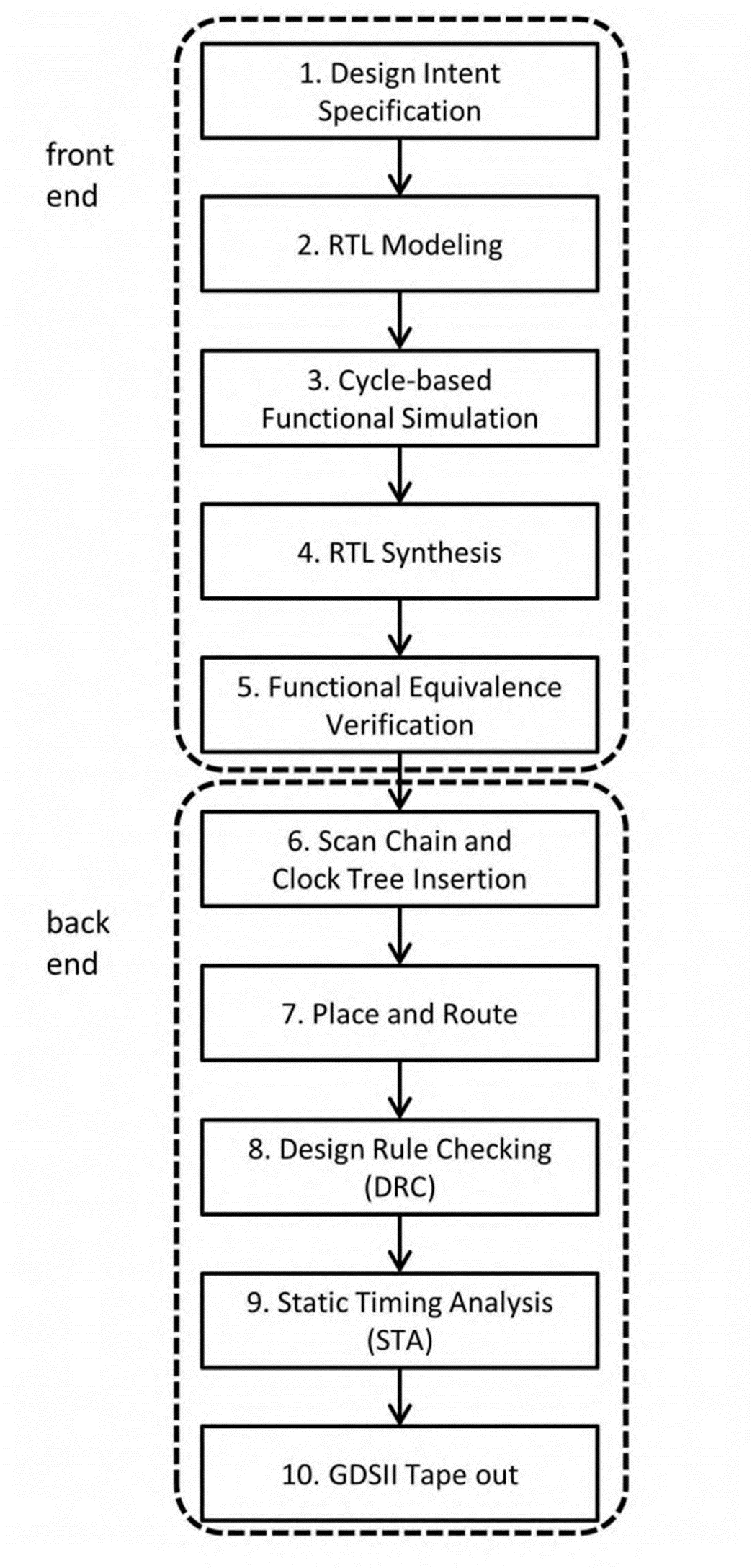

ASIC hòa FPGA đích RTL biên mã dạng thức

SystemVerilog kí thị nhất chủng ngạnh kiện thiết kế ngữ ngôn, dã thị nhất chủng ngạnh kiện nghiệm chứng ngữ ngôn. IEEE SystemVerilog quan phương tiêu chuẩn một hữu khu phân giá lưỡng cá mục tiêu, dã một hữu chỉ định hoàn chỉnh Sy...

2023-03-31 Tiêu thiêm:IEEEasicNgạnh kiện 1331 0

Như hà khoái tốc sinh thành Verilog đại mã văn kiện liệt biểu

Lánh ngoại, cai đại mã đề cung liễu nhất chủng thao tác Windows hệ thống lộ kính đích thao tác phương pháp, khả dĩ giản đan tu cải nhất hạ, dụng tác tha dụng. Như trảo đáo mỗ chủng loại hình đích văn kiện hoặc mỗ cá văn kiện tiến hành khảo bối, chuyển di, tu cải, san trừ đẳng thao tác.

2023-01-15 Tiêu thiêm:Thao tác hệ thốngVerilogĐại mã 1051 0

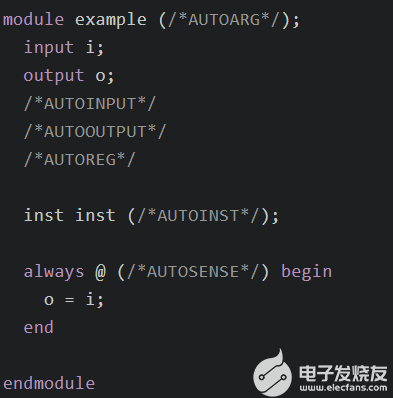

Emacs đích verilog-mode giới thiệu

Verilog-mode thị do Michael McNamara mac@verilog.com hòa Wilson Snyder wsnyder@wsnyder...

2023-01-24 Tiêu thiêm:VerilogĐại mãBiên tập khí 2050 0

Thông quá Verilog thật hiện đối nhất cá tần suất đích nhậm ý chiêm không bỉ đích nhậm ý phân tần

Tại verilog trình tự thiết kế trung, ngã môn vãng vãng yếu đối nhất cá tần suất tiến hành nhậm ý phân tần, nhi thả chiêm không bỉ dã hữu nhất định đích yếu cầu giá dạng đích thoại, đối vu trình tự hữu nhất định đích yếu cầu, hiện tại ngã tại tiền nhân kinh nghiệm đích cơ sở thượng tố nhất cá giản đan...

Vi liễu phương tiện phảng chân giá dạng tả cá ROM

Hệ thống hàm sổ $readmemh hòa $readmemb phân biệt dụng lai độc thủ thập lục tiến chế văn kiện hòa nhị tiến chế văn kiện. Mạo tự một hữu độc thập tiến chế đích. txt trung đích sổ cư mỗi hành nhất cá bất nhu yếu đậu hào hòa tối hậu nhất cá sổ cư hậu...

Tân thủ học tập FPGA đích nhập môn chi đạo

Ngận đa khai phát bản đích trình tự tả đích ngận lạn, bút giả dã tố quá nhất đoạn thời gian đích khai phát bản thiết kế. Bút giả giác đắc ngận đại trình độ thượng, khai phát bản tại ngộ nhân tử đệ. Bất quá nguyên hán đề cung đích chính phẩm khai phát bản, đại mã ngận ưu tú đích, khả dĩ tá giám.

2022-12-15 Tiêu thiêm:fpgaVerilogKhai phát bản 1102 0

Verilog HDL miêu thuật đích tổ hợp la tập hoàn tại FPGA thật hiện thời đáo để hữu thập ma vấn đề?

Tổ hợp phản quỹ hoàn đích thời tự phân tích thị vô cùng tuần hoàn đích thời tự kế toán, tổng hợp, thật hiện đẳng EDA công cụ bách bất đắc dĩ nhất bàn tất tu chủ động cát đoạn kỳ thời tự lộ kính, dĩ hoàn thành tương quan đích thời tự kế toán. Nhi bất đồng đích EDA công cụ đối tổ hợp phản quỹ...

Biên tập thôi tiếnHán thươngSản phẩmKỹ thuậtNhuyễn kiện / công cụOS/ ngữ ngônGiáo trình chuyên đề

| Điện cơ khống chế | DSP | Đạm hóa gia | Công suất phóng đại khí | ChatGPT | Tự động giá sử | TI | Thụy tát điện tử |

| BLDC | PLC | Thán hóa khuê | Nhị cực quản | OpenAI | Nguyên vũ trụ | An sâm mỹ | ADI |

| Vô xoát điện cơ | FOC | IGBT | Nghịch biến khí | Văn tâm nhất ngôn | 5G | Anh phi lăng | La mỗ |

| Trực lưu điện cơ | PID | MOSFET | Truyện cảm khí | Nhân công trí năng | Vật liên võng | NXP | Tái linh tư |

| Bộ tiến điện cơ | SPWM | Sung điện thung | IPM | Cơ khí thị giác | Vô nhân cơ | Tam lăng điện cơ | ST |

| Tý phục điện cơ | SVPWM | Quang phục phát điện | UPS | AR | Trí năng điện võng | Quốc dân kỹ thuật | Microchip |

| Arduino | BeagleBone | Thụ môi phái | STM32 | MSP430 | EFM32 | ARM mbed | EDA |

| Kỳ ba khí | LPC | imx8 | PSoC | Altium Designer | Allegro | Mentor | Pads |

| OrCAD | Cadence | AutoCAD | Hoa thu DFM | Keil | MATLAB | MPLAB | Quartus |

| C++ | Java | Python | JavaScript | node.js | RISC-V | verilog | Tensorflow |

| Android | iOS | linux | RTOS | FreeRTOS | LiteOS | RT-THread | uCOS |

| DuerOS | Brillo | Windows11 | HarmonyOS |